工具/软件:

您好 TI 支持部门、

我有一个关于 LMK04828B IC 的 PLL1 和 PLL2 的问题。

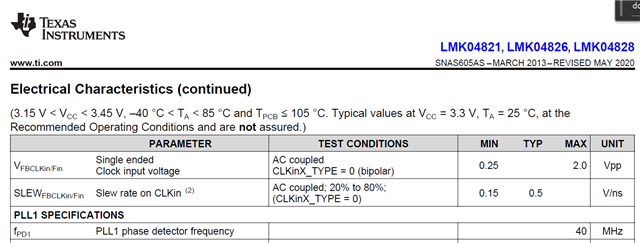

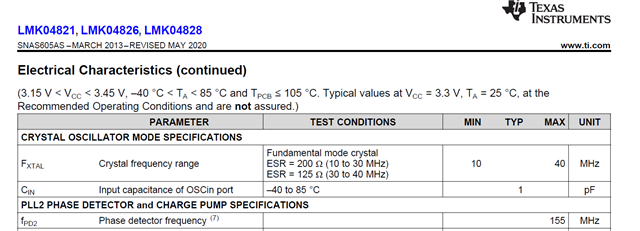

根据规格、PLL1 相位检测器频率规格为 40MHz 最大值、而 PLL2 相位检测器频率为 155MHz 最大值

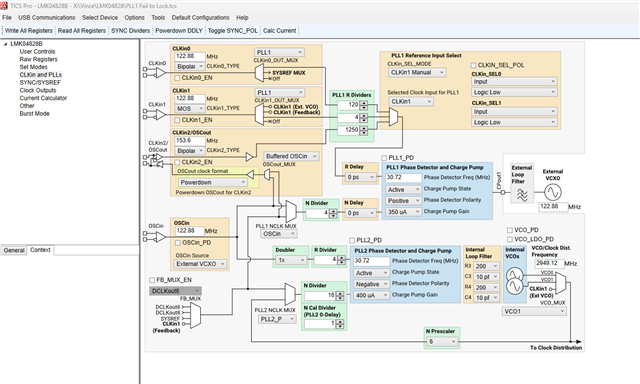

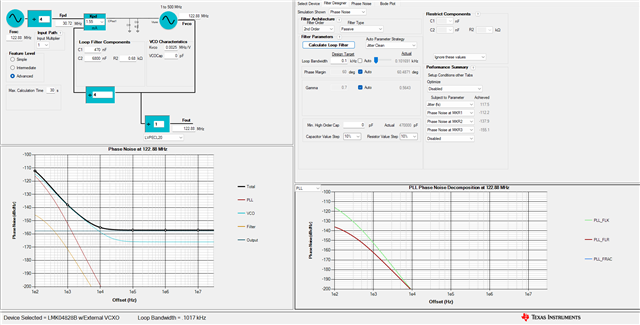

但是、我只设法将它们配置为超出规格以获得 PLL 锁定(即 PLL1 和 PLL2 相位检测器@ 122.88MHz 和)。

我为确保 PLL1 和 PLL2 检测器处于规格范围内所做的任何其他配置都会导致 PLL1 无法锁定。

我能否检查数据表中是否存在解释我所看到行为的错误(或我的旧版本)?

随附的一些 TIcProSW 配置文件展示了 PLL1 和 PLL2 锁定(请参阅“PLL1_PLL2_Locks.TCS")“)和 PLL1 无法锁定(请参阅“PLL1 Fail to Lock.tcs“)的配置。

我试图了解差异在哪里、或者缺少一些解释我所看到行为的信息。

感谢您提供的任何帮助。

谢谢你。

此致

Taie2e.ti.com/.../PLL1_5F00_PLL2_5F00_Locks.tcse2e.ti.com/.../PLL1-Fail-to-Lock.tcs