请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMX2594工具/软件:

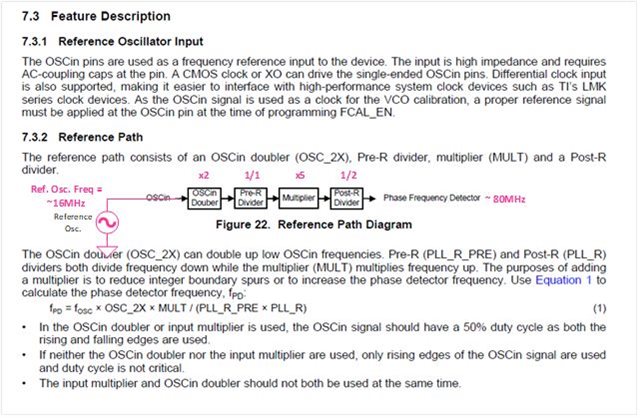

我将 使用 LMX2594 PLL IC 创建原型接收器板。 我的晶体

基准振荡器频率略高于 16MHz。 对于接收器频率计划、我需要

对 PFD 使用~ 80MHz 比较频率。 我可以通过将乘法器设置为来实现这一点

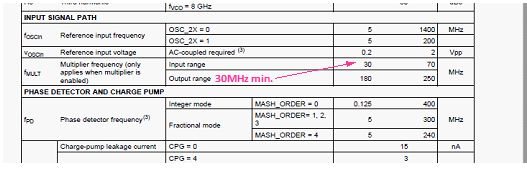

X5. 但是、我注意到了倍频器的最低输入频率要求

为 30MHz。 我是否可以设置如下所示的基准路径并满足乘法器要求

实现目标 PFD 频率时的输入频率要求?