工具/软件:

您好:

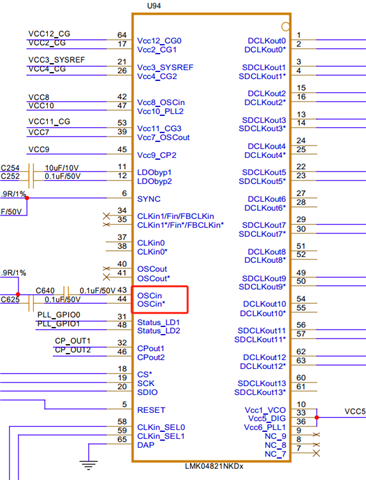

客户希望在多个电路板之间实现 LMK04828 输出时钟的相位同步、但相位始终随机变化。

同步方案(状态):125m 输入由每个电路板上的另一个模块提供、并通过开关连接这些模块、以确保 125m 基准时钟输入来自同一源并进行同步;我们在多个电路板之间进行同步的解决方案是通过 SYNC 引脚发送脉冲以实现同步。 具体方法是通过外部信号源同时向两个电路板发送触发信号。 当 FPGA 检测到该信号时、将发出 ENABLE。 在使能的有效期间、当检测到 125m 时钟模块发送的 1pps 信号时、逻辑中的这两个信号彼此同相、以及在多个电路板中将其用作 04828 的同步事件后的新信号(同步事件的精度无法达到 ps 级)

我们现在主要关心的是知道我们目前的解决办法是否可行。 如果是、应在哪个阶段提供 SYNC 信号?应如何配置寄存器?

我现在已经尝试并发现、当我提供 SYNC 信号时、我通过示波器在两个电路板上观察到 04828 处的系统参考信号输出、发现没有操作。 因此、我不确定我们的解决方案是否可行、或者在配置过程中是否存在问题。 我希望就这一问题提供指导。