Other Parts Discussed in Thread: CDCLVP1204

工具/软件:

您好:

我正在更新一个设计、想将 CDCLVP1204 的未使用输出 (Vcc = 3.3V) 连接到 1.2V 组中 Altera Agilex 7 FPGA 上的差分时钟输入。 这是 50MHz 时钟。

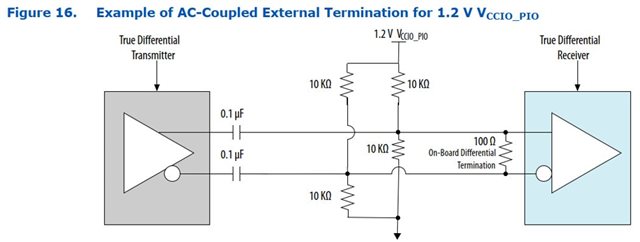

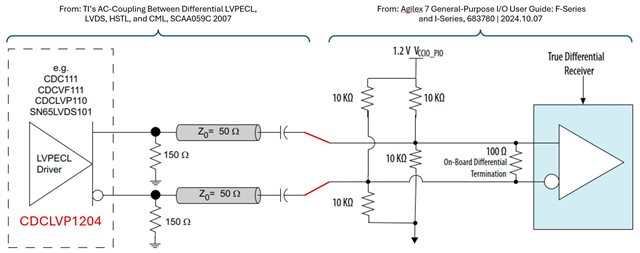

图自:Agilex 7 通用 I/O 用户指南:F 系列和 I 系列、683780 | 2024.10.07

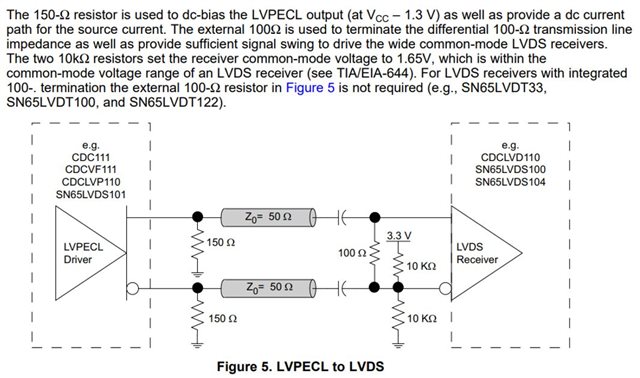

图(从中):TI 的差分 LVPECL、LVDS、HSTL 和 CML SCAA059C–2007 之间的交流耦合

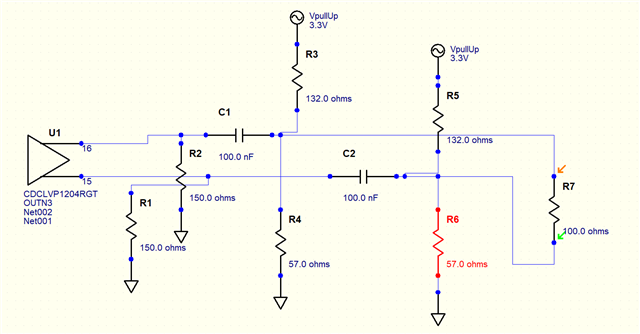

合并图:

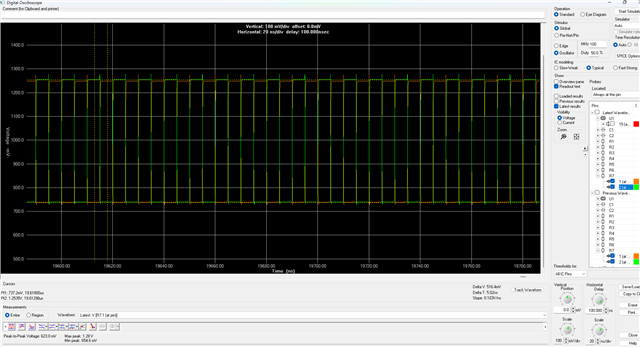

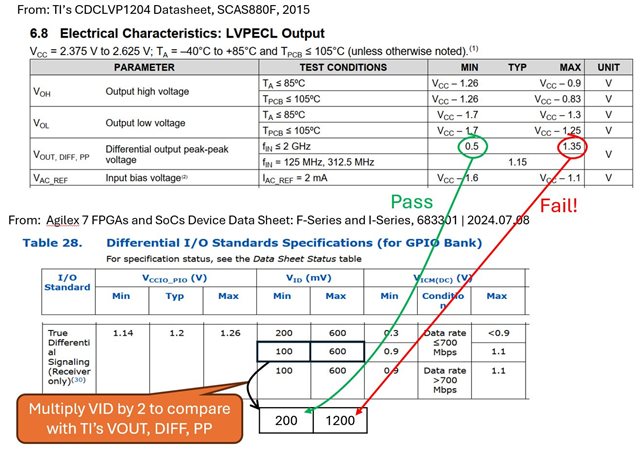

显示数字不起作用的图像:

您能否提供将两者进行连接的建议? 分压器方案呢?

谢谢、

Rob