Other Parts Discussed in Thread: CDCE6214

主题中讨论的其他器件:CDCE6214

工具/软件:

您好论坛、

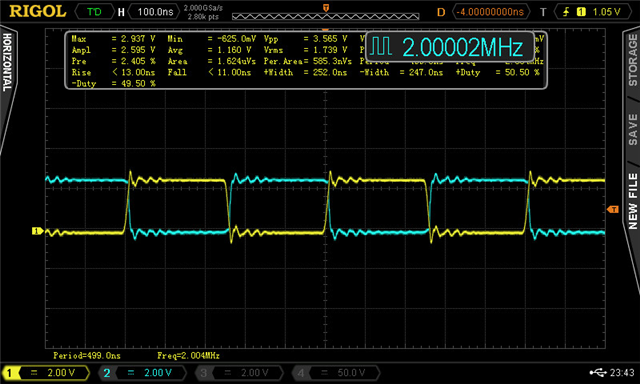

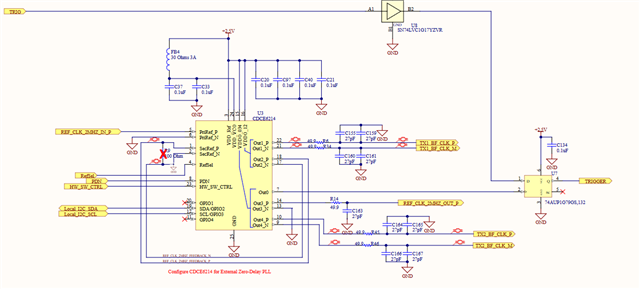

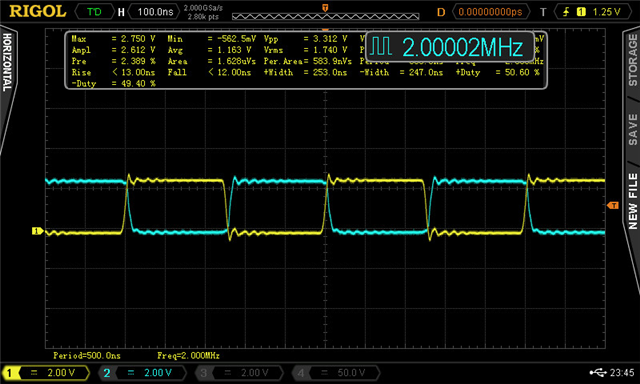

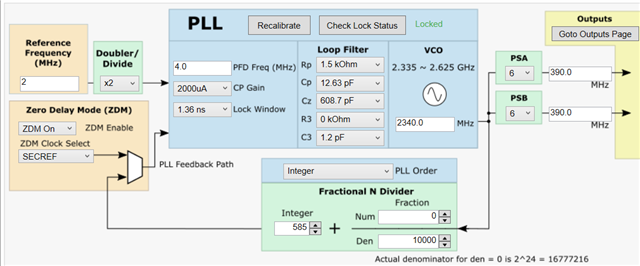

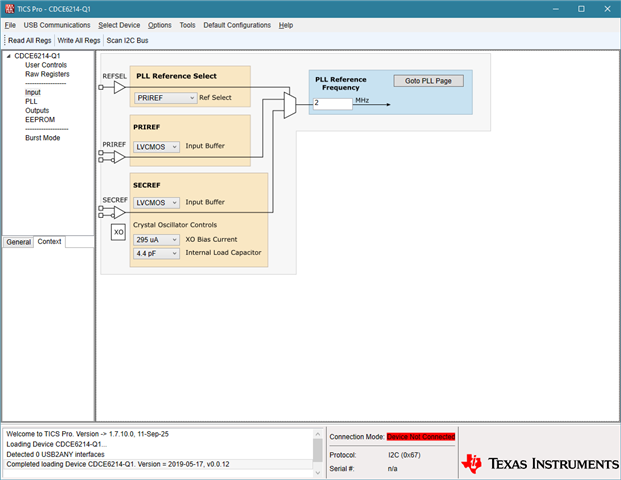

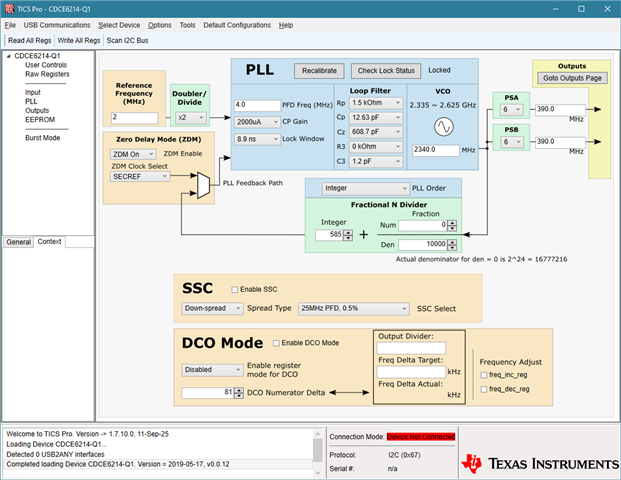

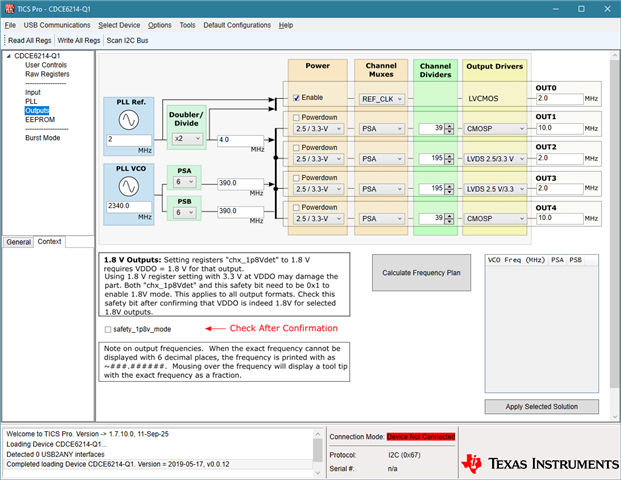

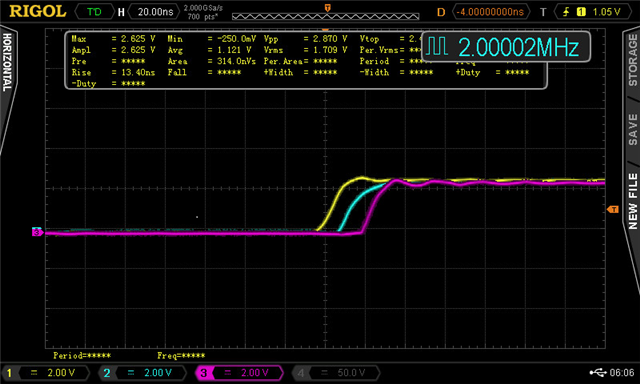

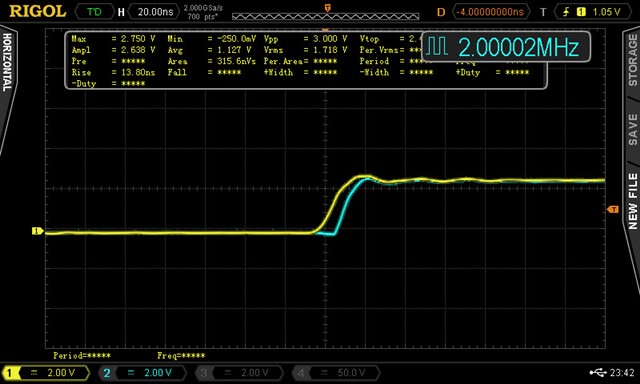

以上是时钟 IC 的当前实现。 我们正在获得正确的输出频率、但输出反相或具有 180 度的相位差。 我们使用 OUT3 来驱动下一个 板时钟芯片、下面是来自第一个板的基准时钟(黄色信号)、而 OUT3(蓝色信号)用于驱动下一个板上的 pri 基准输入。

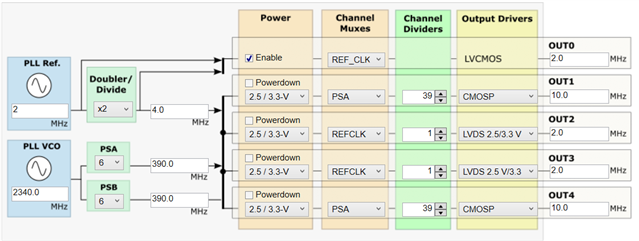

启用零延迟模式、下面是寄存器设置。

e2e.ti.com/.../8880.HexRegisterValues.txt

我们需要使输入 2MHz 信号输入和输出同相。 是否有办法做到这一点?

谢谢您、

乔治·维格莱特

尊敬的 Kadeem:

尊敬的 Kadeem: