请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2571-LMX2571 EP尊敬的团队:

以下是 406.025Mhz 的 PLL 配置。 使用 20Mhz 振荡器(希望评估板中有 20MHz 振荡器)

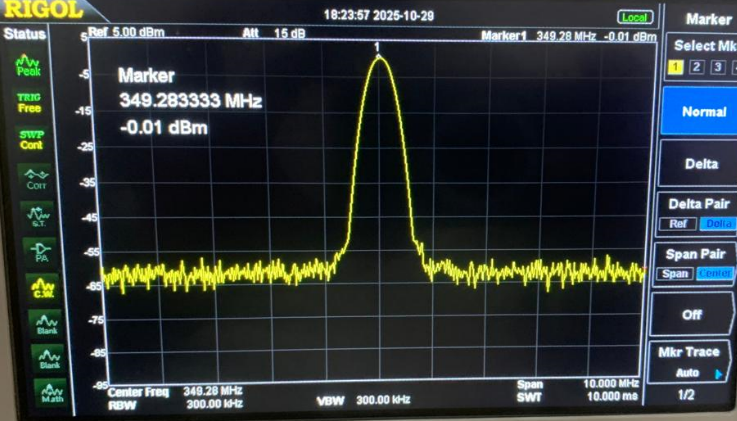

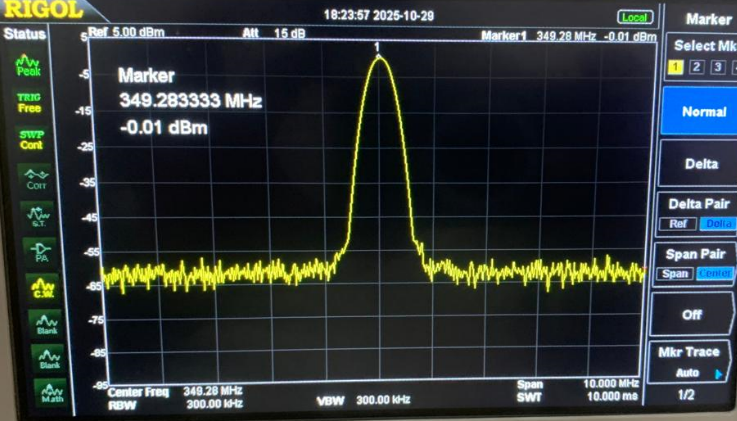

但是,它是锁定在 349.2833Mhz @ 0.01dBm.

让我知道需要完成。

谢谢

--

John

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

以下是 406.025Mhz 的 PLL 配置。 使用 20Mhz 振荡器(希望评估板中有 20MHz 振荡器)

但是,它是锁定在 349.2833Mhz @ 0.01dBm.

让我知道需要完成。

谢谢

--

John

您好、John:

在 GUI 中、将其设置为整数模式、因此分数将被忽略。 如果锁定、它将锁定到 4872MHz。 对于分数通道、应将 FRAC_ORDER 设置为二阶、三阶或四阶。

如果您使用的是 EVM 且没有修改环路滤波器、恐怕即使您使用了正确的 FRAC_ORDER、它也无法锁定。 这是因为 环路滤波器设计为适用于 80MHz Fpd、而您的配置的 Fpd = 0.666MHz。 环路滤波器在这个 FPD 下不再稳定。

如果 fPD = 0.6666MHz 是您的应用要求、则需要重新设计环路滤波器。 您可以使用 PLL Sim (www.ti.com/.../PLLATINUMSIM-SW) 设计环路滤波器。