Other Parts Discussed in Thread: CDCE6214, LMK3H2104

主题中讨论的其他器件: LMK3H2104

工具/软件:

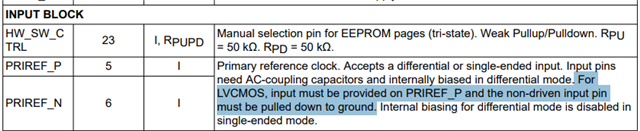

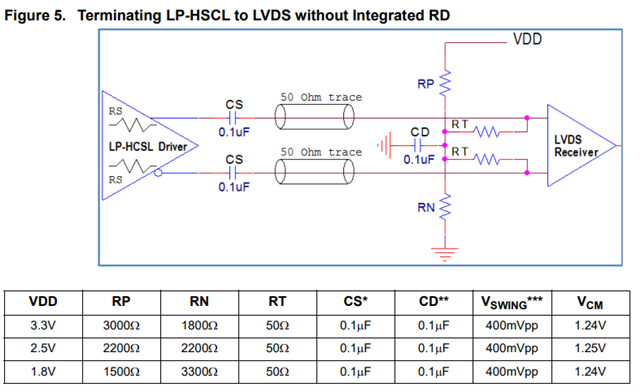

我们计划使用 CDCLVC1310RHBR 作为输入源 CDCE6214RGET (配置为 PCIe 时钟生成)。 两个器件都通电 1.8V 。

您能否确认:

- 在 1.8V 电压下将 CDCLVC1310RHBR 输出直接连接到 CDCE6214RGET 输入是否安全?

- 此配置是否有任何已知问题或建议?

谢谢、

Pradeepraj M