器件型号: LMK1D2108

尊敬的 TI-Forum:

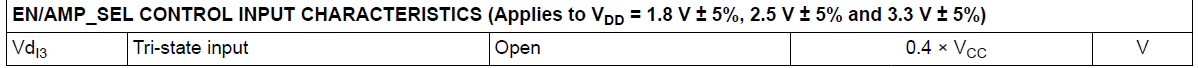

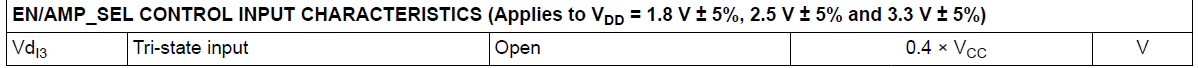

当组 0 使用 3.3V 电压、组 1 使用 1.8V 电压时、我想知道 AMP_SEL 的上拉电阻使用哪个电源。 1.8V 的电压略大于 0.4 x 3.3 = 0.54V、应该可以工作、但 3.3V 是否会损坏某个器件?

谢谢你。

此致

Moritz

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: LMK1D2108

尊敬的 TI-Forum:

当组 0 使用 3.3V 电压、组 1 使用 1.8V 电压时、我想知道 AMP_SEL 的上拉电阻使用哪个电源。 1.8V 的电压略大于 0.4 x 3.3 = 0.54V、应该可以工作、但 3.3V 是否会损坏某个器件?

谢谢你。

此致

Moritz

尊敬的 Moritz:

我咨询了我们的设计团队、他们确认 EN 引脚连接到 VDDB、AMP_SEL 引脚连接到 VDDA。

需要注意的另一点是、VDDA 和 VDDB 都必须高于 2.1V 才能获得 1.2V 的标准 LVDS 输出共模。 例如、如果 VDDA = 1.8V 和 VDDB = 3.3V、两个输出组将具有大约 1.1V(典型值)的相同共模。 如果您的应用不需要担心这一点、可以为每个组使用不同的电源电压。 是否有任何特殊原因在您的用例中为 VDDA 使用 3.3V 电压并为 VDDB 使用 1.8V 电压?

此致、

Connor