Other Parts Discussed in Thread: CDCLVP111-SP, CDCM7005-SP, LMK04832, LMK61E2, ADC3683, LMX2615-SP

器件型号: LMK04832

Thread 中讨论的其他器件: LMK61E2、 ADC3683、CDCLVP111-SP、 LMX2615-SP、CDCM7005-SP

尊敬的所有人:

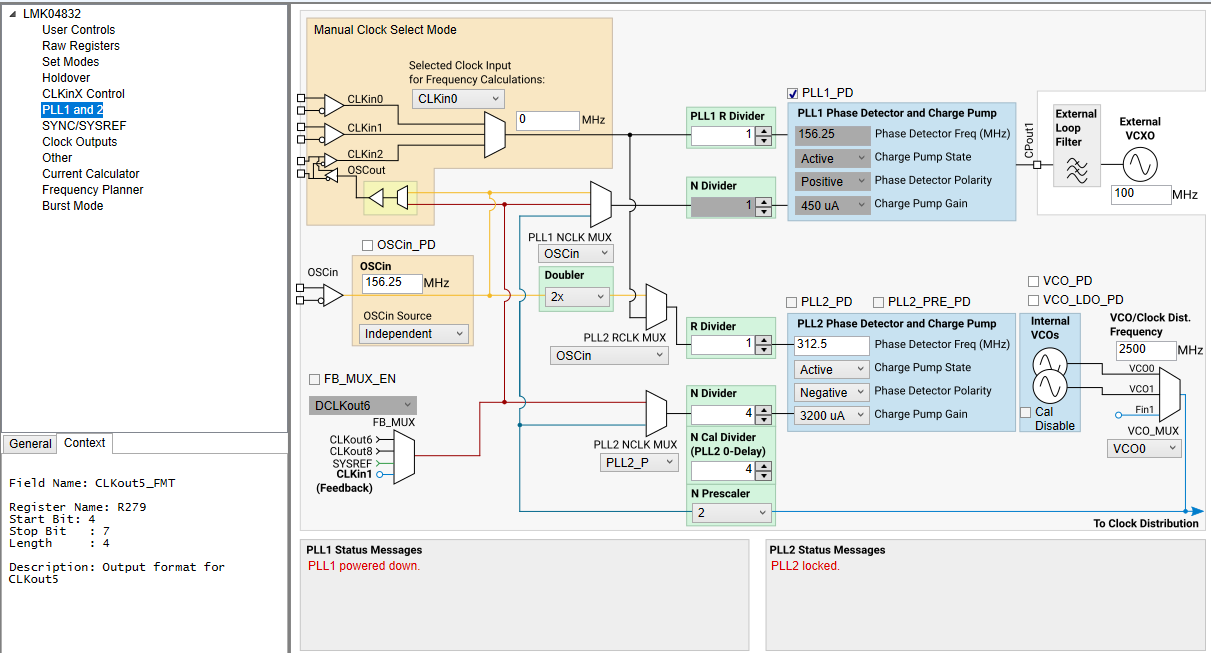

我将 LMK61E2 与 LMK04832 配合使用、为七个 ADC3683 供电。 LMK61E2 应为 LMK04832 生成 156.25MHz、然后生成 62.5MHz 和 312.5MHz 两个时钟、分别作为 ADC3683 的采样频率 (CLK) 和数字接口时钟 (DCLKIN)。

TICS Pro 中的结构如下所示:

和

PLLatinumSim 中的建模看起来像这样(考虑 CPout2 上的 60 pF 内部电容):

LMK61E2 的相位噪声如下所示:

问题:

.:您认为所选的结构对于七个 ADC3683 芯片的时钟生成是合理的吗? 尤其是在偶数输出上生成 62.5MHz 和在奇数输出上生成 312.5MHz 是可以接受的吗? 还是您认为它有问题? 我找不到任何其他配置、如何使用单个 LMK04832 来生成这两个时钟。

.:由于 62.5MHz 和 312.5MHz 不需要进行相位同步来实现 ADC3683 的正常运行,您是否认为,由于相邻时钟输出上可能存在串扰,选择两个独立的时钟发生器 IC 可能更明智? 一个使用 62.5MHz 时钟生成七个输出、其他七个使用 312.5MHz 生成? 如果这种方法更好、您能否推荐特定的 IC、该版本还具有符合空间要求的版本?

.:我关心相位噪声特性,我尽量减少。 你认为它可能仍然是可能挤压频率特性在 PLLatinumSim 下面一点?

非常感谢您的支持!

此致、

Ondrej