器件型号: AM6442

您好:

我尝试通过更新 DTS 中的时钟频率(或 bus_freq)属性、为我们的定制电路板(AM642 处理器)上的以太网控制器 (CPSW 和 ICSSG) 设置特定的 MDC 总线频率。

最初、MDC 总线频率设置为 1MHz 、但示波器 的测量结果为 CPSW ~500kHz、 ICSSG 的测量结果为~700kHz。

稍后、我更改了 DTS、以便 为两条总线请求 300kHz、现在驱动程序用以下命令在内核中报告所请求的频率:dmesg | grep -i mdio:

[ 2.038840] davinci_mdio 300b2400.mdio:DaVinci MDIO 修订版 1.7、总线频率 300000

[ 2.23487] davinci_mdio 8000f00.mdio:DaVinci MDIO 修订版 9.7、总线频率 300000

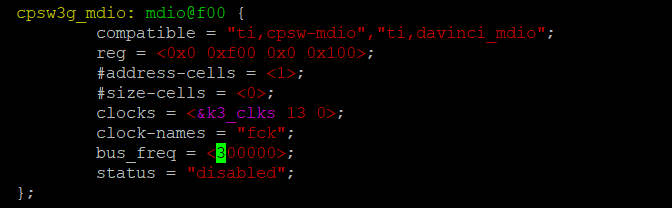

对于 300kHz 配置、k3-am64-main.dtsi 中所做的更改如下:

但是、在示波器上进行测量时、MDC 时钟仍显示相同的速率 — CPSW 约 为 500kHz、ICSSG 约为 700kHz。

我想提供有关应在何处确切配置 MDC 时钟频率的指导、以便:

硬件反映了所请求的频率。

驱动程序在探测过程中正确读取它。

SDK 版本:tisdk_10.00.07.04

Linux 内核版本:6.6.32

提前感谢您提供的任何建议。