Other Parts Discussed in Thread: LMX2820EVM, LMX1204EVM, LMX1204, LMX2820

器件型号: LMX2820EVM

主题中讨论的其他器件: LMX1204EVM、 LMX1204、 LMX2820

您好、

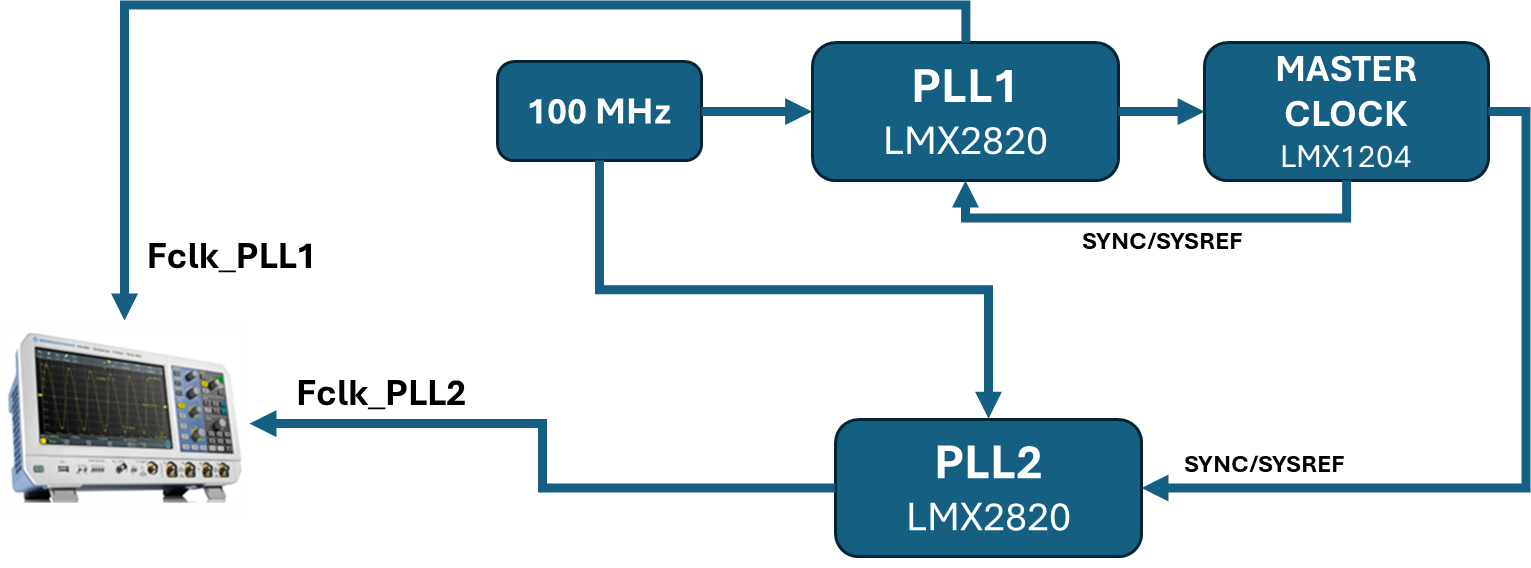

我正在尝试同步两个 PLL LMX2820EVM、如下图所示:

- 工作频率范围 同步类别 2 。

- 设计思路是使用 LMX1204EVM 的 SYSREF 输出 用作 PLL 的同步信号。 SYNC/SYSREF 输出将在内部生成到 LMX1204EVM。

- PLL 同步后、 LMX1204 生成的同步信号将编程为的 SYSREF 输入(可能会更改频率) PLL2820EVM 、然后将在中继器模式下使用。

我想知道这种架构是否可行、主要挑战是什么、以及应如何配置 PSYNC 引脚 (和相关电阻)使其正常工作。

提前感谢您的支持。

此致、

Ferdinando