Other Parts Discussed in Thread: LMX2694-SEP, LMX2571

器件型号: LMX2694-LMX2694-LMX2694-LMX26146- EP

主题中讨论的其他器件: OPA211-OPA211 EP、 LMX2571-LMX2594-SEP EP

您好:

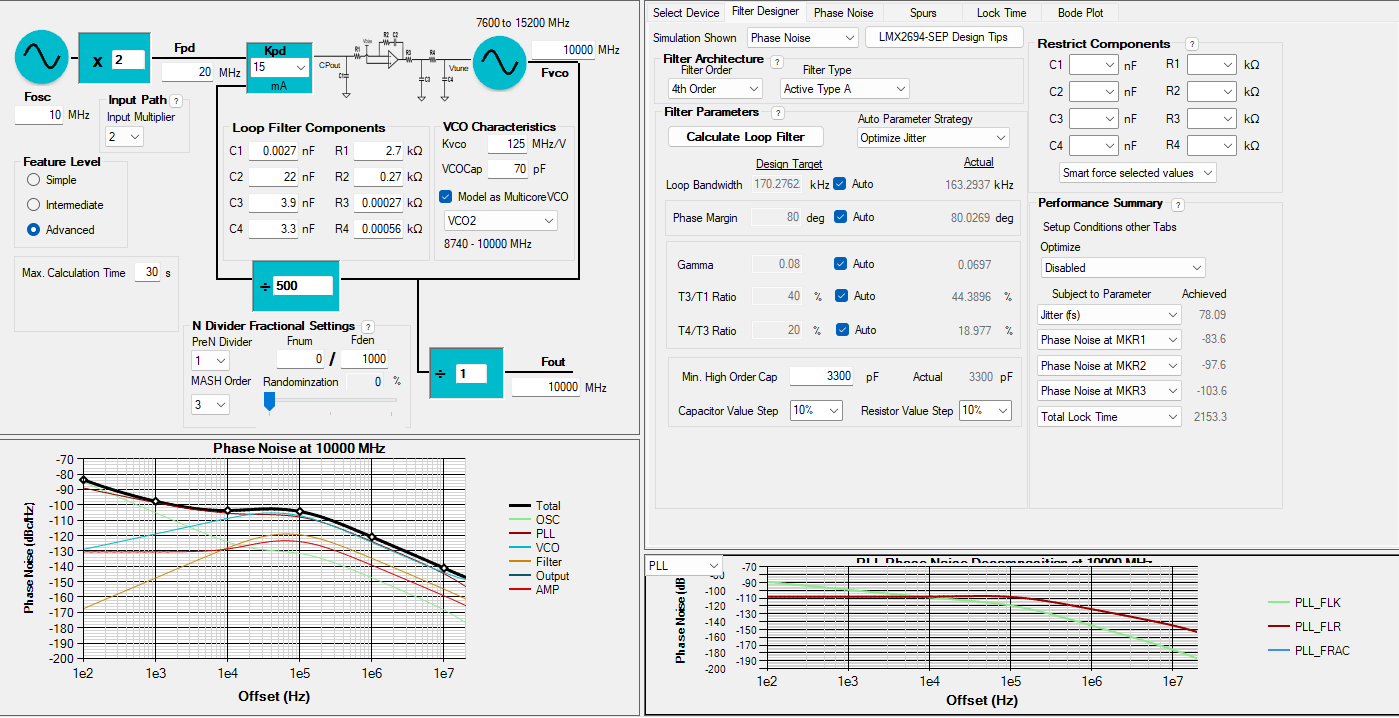

我目前正在设计一个 PLL、用于分别将 10MHz 基准上变频为 5000MHz 以及 10000MHz ADC 和 DAC 基准时钟。 我在 10000MHz 上附上了一张 PLL 设计图像。 但我应该注意的是、我确实打算使用 A 型有源滤波器、但我想使用 EP、它具有 1.1nV/√Hz 的出色噪声特性。

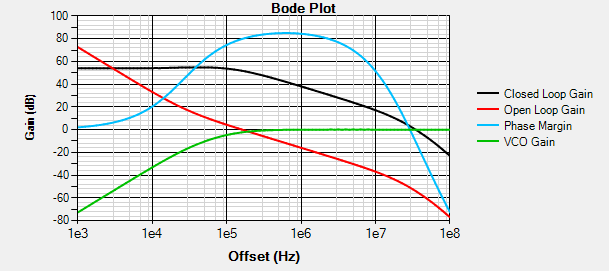

我认为我已经将环路带宽、相位裕度和相位噪声明白到我的设计可接受的水平、但我不确定稳定性波特图。 请参阅以下内容。

我知道相位裕度设计可能过大、但是、我担心相位裕度在超过 2MHz 偏移后会急剧滚降。 有人能为我所描述的应用提供一些关于合适波特图设计的指导、以及关于改进整体设计的一般建议(如果适用)吗?

谢谢您、

Joseph Blank