团队,

请回答我客户的问题:

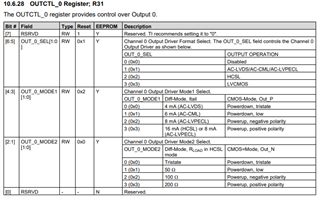

我的 LMK03318RHS 与另一个 TI 部件一起设计,而另一个部件的数据表表明,在电源关闭时,其时钟输入必须保持三个声明。 接收时钟的部件的输入是 LVDS,因此我打算将 LMK03318RHS 的输出设置为 LVDS 模式,但在接收部件通电时禁用, 然后,LMK03318RHS 的时钟输出将在接收器通电且稳定后启用。 我认为,LMK03318RHS 支持此操作,即设备的输出通道可以单独控制,而配置为 LVDS 的输出通道可以三种形式声明,但我希望确保我正确读取了 LMK03318RHS 的数据表。

我‘,该操作由 LMK03318RHS“OUTCTL_0寄存器”控制;例如,R31”用于输出0,这是正确的,并且该部件能够在 LVDS 模式下三次声明其输出。 那么,LMK03318RHS 是否可以像我所描述的那样进行控制?在禁用和 LVDS 模式下,各个信道是否真正具有三个信号?

谢谢

维克托里亚