This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

维克多

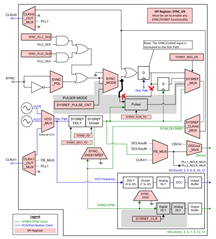

数据表图中的唯一错误是脉冲串触发器路径应直接连接到或门之前的 SYNC_MODE mux 输出。 通过 SYSREF_MUX,CLKin0和 SYSYNC_MODE 都被重新计时到“正常同步”路径上的时钟分配路径。 CLKin0还可以绕过重计时器,并通过更改 SYSREF_CLKin0_MUX 设置直接分配到 SYSREF 分布路径。

我可以预测一些后续问题:

我们有一些数据表明,同步引脚与时钟分配路径的正时仅可靠到大约3-5 ns,并且在温度和电源电压方面会相差超过1 ns。 同步引脚定时的电路主要是 CMOS,它具有相当大的温度相关性。 如果您只需要在一台设备上进行输出对齐,同步引脚计时就不是问题。 使用同步引脚 尝试将多个设备(或一个具有基本输入到输出相位关系的设备)与时钟分布路径上的 GHz VCO 同步,基本上可以保证在不利用零延迟模式等更具约束性的配置的情况下失败。

我们还有一些数据表明,CLKin0端口重新定时非常精确,设置时间小于150PS,PVT 的变化非常有限。 此路径全部在专用内部 LDO 上的低漂移和低噪声双极电路中完成, 这 对计时变化的影响要小得多。 因此,如果您尝试与 GHz VCO 进行精确或多设备同步, 由于无法使用任何策略来增加有效的同步窗口(例如,使用 SYSREF 分隔器的零延迟模式来利用第二个 DFF 重计时器),CLKin0端口是使用的最佳方法,其计时精度将大大优于同步引脚。

有一个应用程序注释讨论 了一些在同步过程中减轻计时负担的方法: https://www.ti.com/lit/pdf/snaa294

同样值得注意的是:一旦 SYSREF 分隔器阶段通过同步过程锁定,SYSREF 分隔器的同步引脚触发(甚至 SPI 触发)通常是您所需要的, 因为 SYSREF 脉冲发生器隐式地重定时到 SYSREF 分隔器边缘,而该分隔器边缘的幅度顺序几乎总是比时钟分布路径频率慢。

此致,

德里克·佩恩