“线程:测试”, LMK04832, USB2ANY, LP3878中讨论的其它部件

您好,

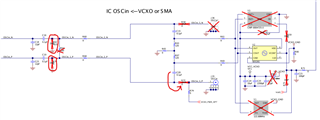

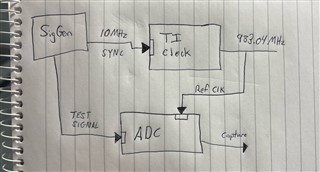

我正在尝试从983.04MHz 中获取时钟,并将此信号同步到10MHz 外部信号。 下面的照片描述了我要执行的设置:

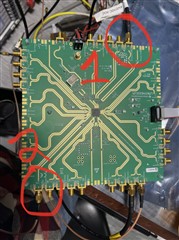

我想知道您是否可以提供配置文件并确认我的硬件设置是否正确。 在硬件照片上,“1”旁边的圆圈是我的 SigGen 的外部参考频率122.88MHz (如用户指南中的建议,上图中未显示)。

硬件照片中“2”旁边的另一个圆圈是同步针脚,我也从 SigGen 中注入了10MHz 外部信号,但我无法锁定 PLL。 任何见解都将受到极大的启发。

KR,

亚历克斯