大家好!

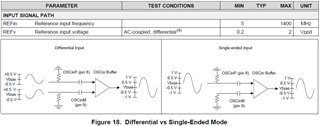

我从数据表中看到 ,只要差分信号的 Vppd 介于0.1到1之间,或者单端信号的 Vppd 介于0.2到2之间,设备就会按照数据表中的定义运行。

从客户对其他 PLL 设计的体验来看,输入功率范围中可能有一个对 器件性能影响不大的亮点。 现在,他们使用100MHz 晶体,但有机会将其更改为150MHz 版本。 在任何一种情况 下,如果确定输入功率的最佳范围,都可以选择将参考功率调整到 LMX2592。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好!

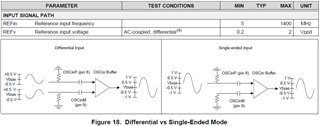

我从数据表中看到 ,只要差分信号的 Vppd 介于0.1到1之间,或者单端信号的 Vppd 介于0.2到2之间,设备就会按照数据表中的定义运行。

从客户对其他 PLL 设计的体验来看,输入功率范围中可能有一个对 器件性能影响不大的亮点。 现在,他们使用100MHz 晶体,但有机会将其更改为150MHz 版本。 在任何一种情况 下,如果确定输入功率的最佳范围,都可以选择将参考功率调整到 LMX2592。

卡梅伦,您好!

我们没有对输入水平与性能进行全面分析,我们不知道是否存在这样一个好地方。 但是,输入电平实际上会影响信号的转换速率,这对 PLL 很重要。 例如,使用10MHz 时钟时,正弦波和方波时钟之间的 PLL 性能有很大差异。 LVDS (方波时钟,400mV)将返回良好的 PLL 性能,但幅度相同的正弦波时钟将返回不良的 PLL 性能。 这是因为雪橇速率非常差。 我们可以增加正弦波信号的振幅以提高其转换速率,这将提高 PLL 性能。

在低频率下,较高的频率(例如100MHz 或150MHz),信号摆幅越高,转换速率越高,改善幅度就越小,因为转换速率已经很好。 将输入从100MHz 移至150MHz 的好处 是我们可以获得更高的 FPD。 在较高的 FPD 下,N 分隔值较小。 因此,PLL 噪声更小。