Other Parts Discussed in Thread: TPL5111

大家好,团队

我的一位客户正在评估 TPL5111的新产品。

此时,客户有以下问题。

请告诉我你的建议。

问题1. 在 DRVn 从 L 升至 H 后,我们希望使用 Delay/M_DRV 终端延长设备间隔时间

是否有任何方法来扩展 DRVn H 级别?

问题2. 当延迟/M_DRV 端子被拉至 VDD 时,DRVn 能否保持水平?

此致。

肯戈。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,肯戈,

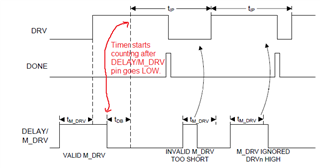

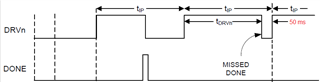

如果未接收到完成信号,则 DRVn 引脚对于叶尖为50毫秒的偏高电压。叶尖由延迟/M_DRV 引脚处的分流电阻器确定。 因此,如果要延长 DRVn 的高时,可以调整分流电阻器值。

我们可以强制 DRV 在延迟/M_DRV 引脚处使用脉冲表示高电压。 延时/M_DRV 变低+20毫秒(TDB)后计时器开始计数。 如果您保持延迟/M_DRV 高,DRV 将保持高电平,且计时器将不会启动,直到延迟/M_DRV 引脚变低。