请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:CDCE925 “线程”中讨论的其它部件:CDCE913

尊敬的各位先生:

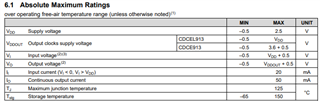

关于电压范围内的 CDCE913 CLK,我们错误地认为它与3.3V 兼容,如本主题所述:

我们的问题是,哪些设计“强制”3.3V 超出串行电阻,并向 CLKIN 引脚输出6 mA 输入电流,这些电流稳定在2.5 V 左右,是否会随着时间的推移而失效?

现在,在发现这一点后,我们已经检查了 Vdd 电压1.8 V,并且稳定,因为据报道,Vdd 的消耗量为每 PLL ~9 mA。 来自该 CDCE 的抖动也符合规格要求。

当然,我们将通过适当的分隔符(源序列和目标并行)终止来纠正这一问题,以平衡线路。

此致,

乌鲁斯