您好,

我的客户正在使用 LMK04826并在以下配置文件中进行设置。

e2e.ti.com/.../lmk04826_5F00_220225.tcs

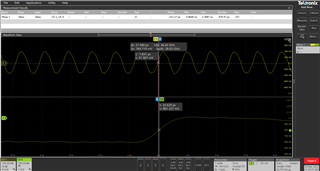

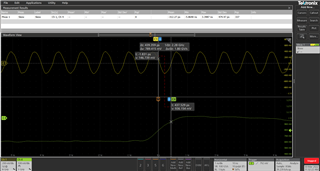

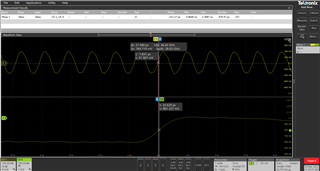

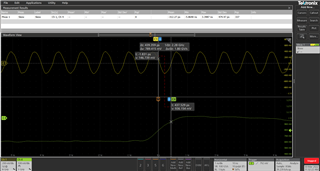

每当它们初始化 LMK04826时,SYSCLK 和 SYSREF 之间的同步会有差异,如下所示。

请检查设备设置以确保 SYCLK 和 SYSREF 始终保持同步。

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我的客户正在使用 LMK04826并在以下配置文件中进行设置。

e2e.ti.com/.../lmk04826_5F00_220225.tcs

每当它们初始化 LMK04826时,SYSCLK 和 SYSREF 之间的同步会有差异,如下所示。

请检查设备设置以确保 SYCLK 和 SYSREF 始终保持同步。

谢谢你。

JH

你好,JH,

现在,不应用同步,输出的分隔器状态将根据 SPI 计时进行初始化,该计时将有很大的不同。 客户是否也有同步过程?

我注意到他们已启用 SYNC_PLL2_DLD。 如果他们希望 PLL2锁生成分隔器重置和同步信号,则必须首先配置同步路径,以接受 PLL2_DLD 作为同步源(SYNC_MODE =1,SYSREF_MUX =0) 并且最初必须为所有参与同步的分禾器使用 SYNC_DISx =0和 DDLY_PD =0对设备进行编程。 最初,输出时钟将保持在复位状态,然后当 PLL2锁定时,复位状态将被释放。 最后,他们可以在 PLL2_DLD 断言后将 SYSREF_MUX 切换到所需的设置。

此致,

德里克·佩恩

JH,

400PS 错误听起来像是同步之间的一个 VCO 周期差。 由于每次 发生同步事件时都应在设备时钟中重置所有固定的数字延迟,因此我唯一能想象到的问题是 SYSREF。 也许他们最初可以尝试使用 SYSREF_CLR=1对设备进行编程,然后在获得锁定后,他们可以在与清除 SYNC_PLL2_DLD=0相同的编程更新中清除 SYSREF_CLR=0。 每个通道上的 SYSREF 本地数字延迟都有一个与固定数字延迟分开的清除机制,该机制可能负责 两个电源周期之间的 VCO 周期差异。

此致,

德里克·佩恩