大家好,

我不太精通PLL。

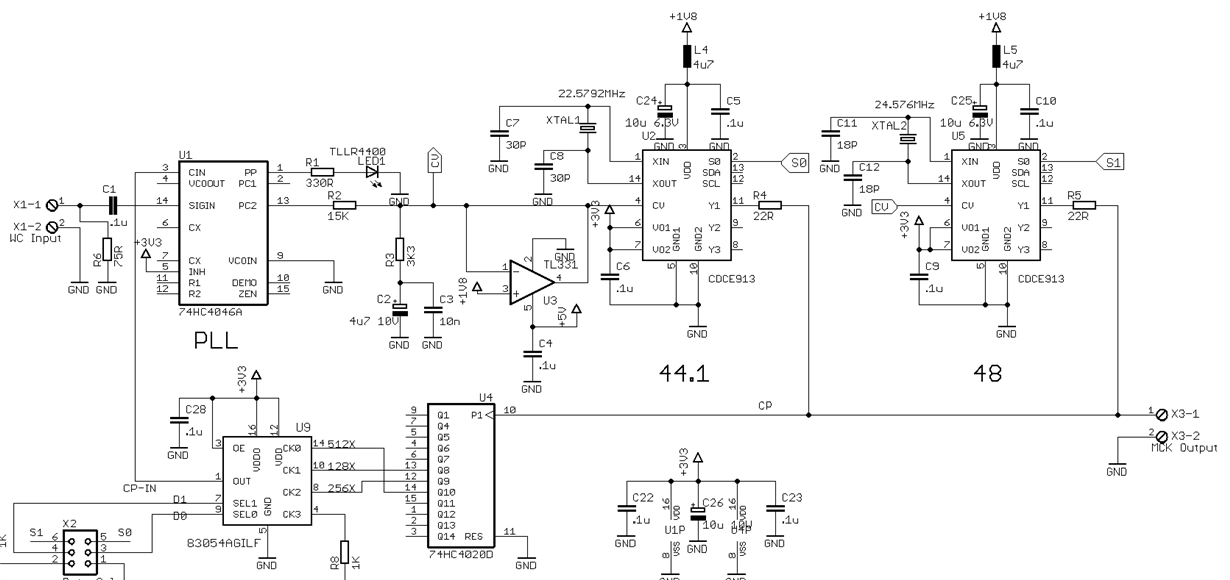

我决定复制"SCAA088 - Generating Clocks for ADC from Word Clock"上的音频时钟设计,我不是使用CDCE内部寄存器(I²C)来划分反馈,

而是4020作为分隔器。 所用的晶体就是 这些。

它们的额定容差和稳定性为±30ppm,C0最大值 7 pF。

我找不到App便笺中建议的内容。

我必须指出,我只使用一个5.6pF校正外部电容器来获得所需的22.5792MHz频率输出。

问题:

CDCE的输出似乎与Word时钟输入不同步。

例如,我从我的范围中获得了一些vid,系统接收44.1kHz字时钟,并输出一个512x FS主时钟,频率为22.5792MHz。

探测:

1.7046 PC 2 输出,引脚13 (相频检测器);

2. LPF输出 - CDCE913 CV输入,引脚4

3. 44.1kHz 时,信号输入(黄色迹线)和COMP输入(蓝色)为7046。

4. 22.5792MHz 时的SIG IN (黄色迹线),44.1k和CDCE913 Y1输出(蓝色)(秒 5,我将触发源更改为Ch2,以显示正确的22.5792MHz计数)。

我注意到,当SIG In没有信号时,CDCE控制电压为0V,而当信号存在时,CV始终为1.8V的最大值。

7046 PFD输出(请参阅第一个vid)的行为异常。 它不应该只有小脉冲?

非常感谢任何建议。

谢谢!

原理图: