请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMK0.461万 您好,

问题1.

LMK0.461万用于为KINTEX7160T FPGA生成200MHz LVDS (4-mA HSDS或6-mA HSDS)系统时钟。 生成的输出时钟具有比正常LVDS规格高得多的差动输出电压摆幅,因此必须在KINTEX7 FPGA输入时设置板载端接。

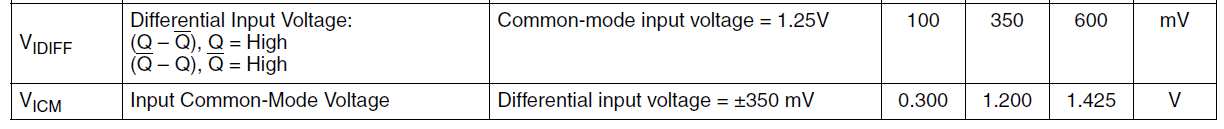

时钟输入的FPGA LVDS规格如下所示

问题2.

100MHz LVCMOS VCXO连接到LMK0.461万的OSCIN针脚。 此100MHz LVCOMS时钟的缓冲副本在OSCOUT引脚处取出,用于FPGA系统时钟的电源。

那么如何处理OSCOUT*引脚(NC或接地)?

提前感谢

Deepak V