主题中讨论的其他部件:TMS320C6678,

我使用CDCM6208 为TMS320C6678生成时钟。 CDCM6208的输入是25MHz晶体连接到SEC_REFP/N

对于Y0/Y1/Y2100MHz,CDCM6208的输出为156.25MHZ,对于Y4/Y5/Y6,Y3和Y7,输出为浮动。 VCO碎片为3.125GHz。实际输出频率为90 % ,符合我的预期,Y0/Y1/Y2约为140MHz,Y4/Y5/Y6约为90MHz。

我尝试更改输出频率,我将 Y0/Y1/Y2更改为125MHz,Y4/Y5/Y6 更改为100MHz,这次VCO频率为3GHz, 而实际 输出频率是 我所期望的94 % ,Y0/Y1/Y2约为118MHz,Y4/Y5/Y6约为94MHz。

我使用osilloscope观察输出频率,尽管频率错误,波形非常稳定。

我配置statuso pin是PLL_LOCK,status0 pin is not pull up。

我 测量CDCM6208的功率,它是3.35V。 我认为权力 是可以的。

我 使用Spartan6 控制带有SPI的CDCM6208,我使用的Verilog代码是OK,因为我使用相同的代码来控制其它主板(称为主板A)的CDCM6208成功生成时钟频率。

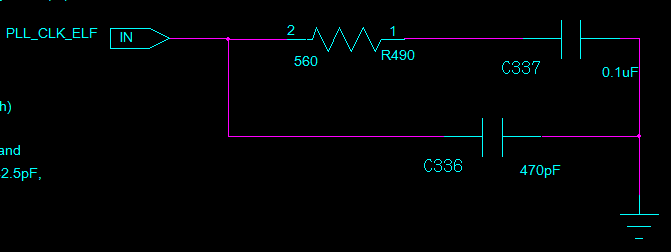

环路滤波器如下所示,与板A相同,

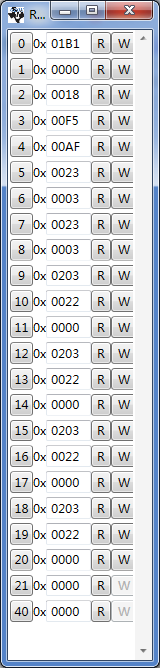

CDCM6208的注册表如下

错误和稳定的输出频率让我困扰了几天,请帮助我。