主题中讨论的其他部件: CODELOADER

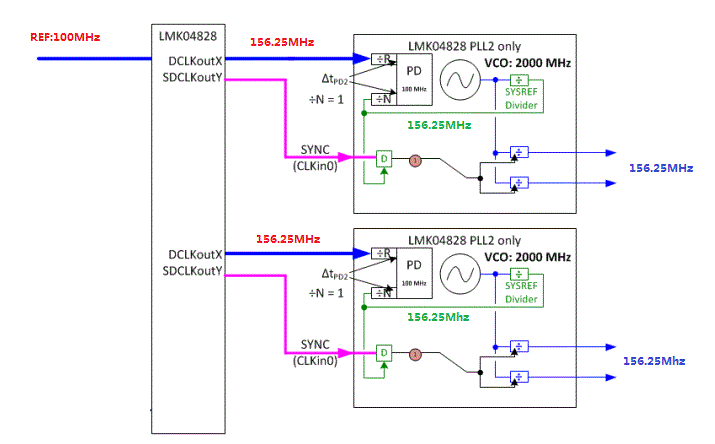

我需要10对DCLK和SYSREF来为10个DAC芯片提供服务。

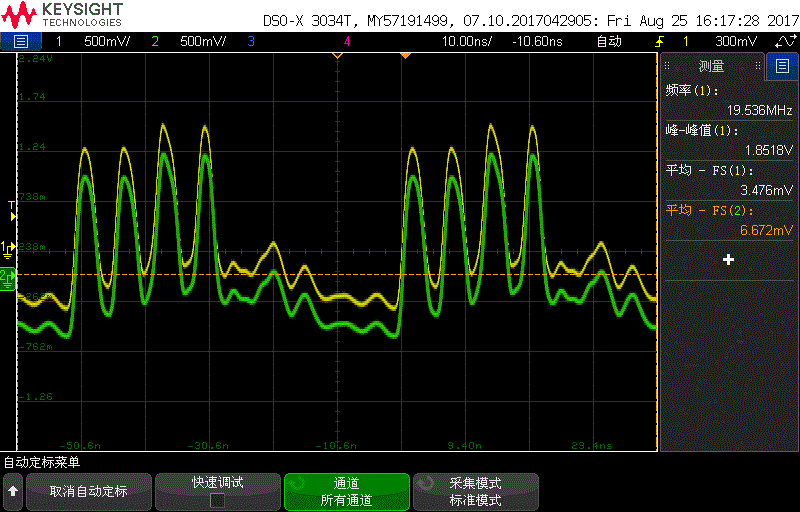

DCLK = 156.25MHz,SYSREF = 19.5.3125万MHz

LMK0.4828万可以提供7对DCLK和SYSREF,所以我需要两个并联的LMK0.4828万。

主参考输入:100MHz,主LMK0.4828万提供156.25MHz DCLK和19.5.3125万MHz SDCLK (连续,用于从属设备的同步输入)

主LMK的SYNC PIN和CLKIN0 PIN未使用

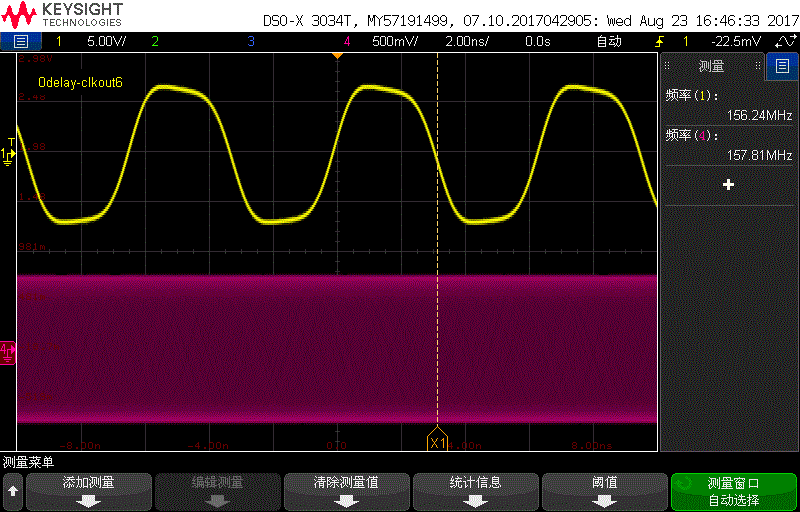

我的问题是:两个从LMK的DCLK输出没有相位对齐。没有SYSREF输出。

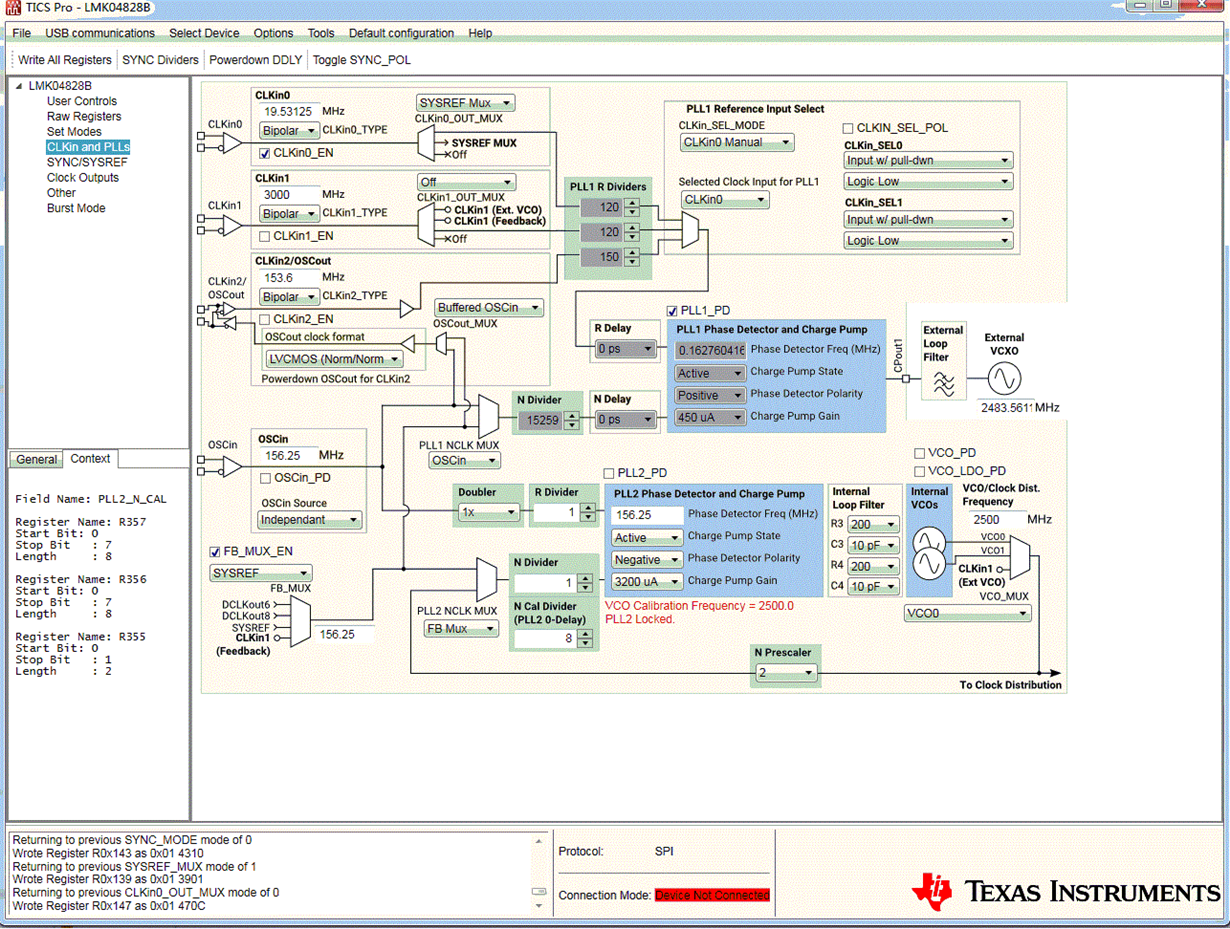

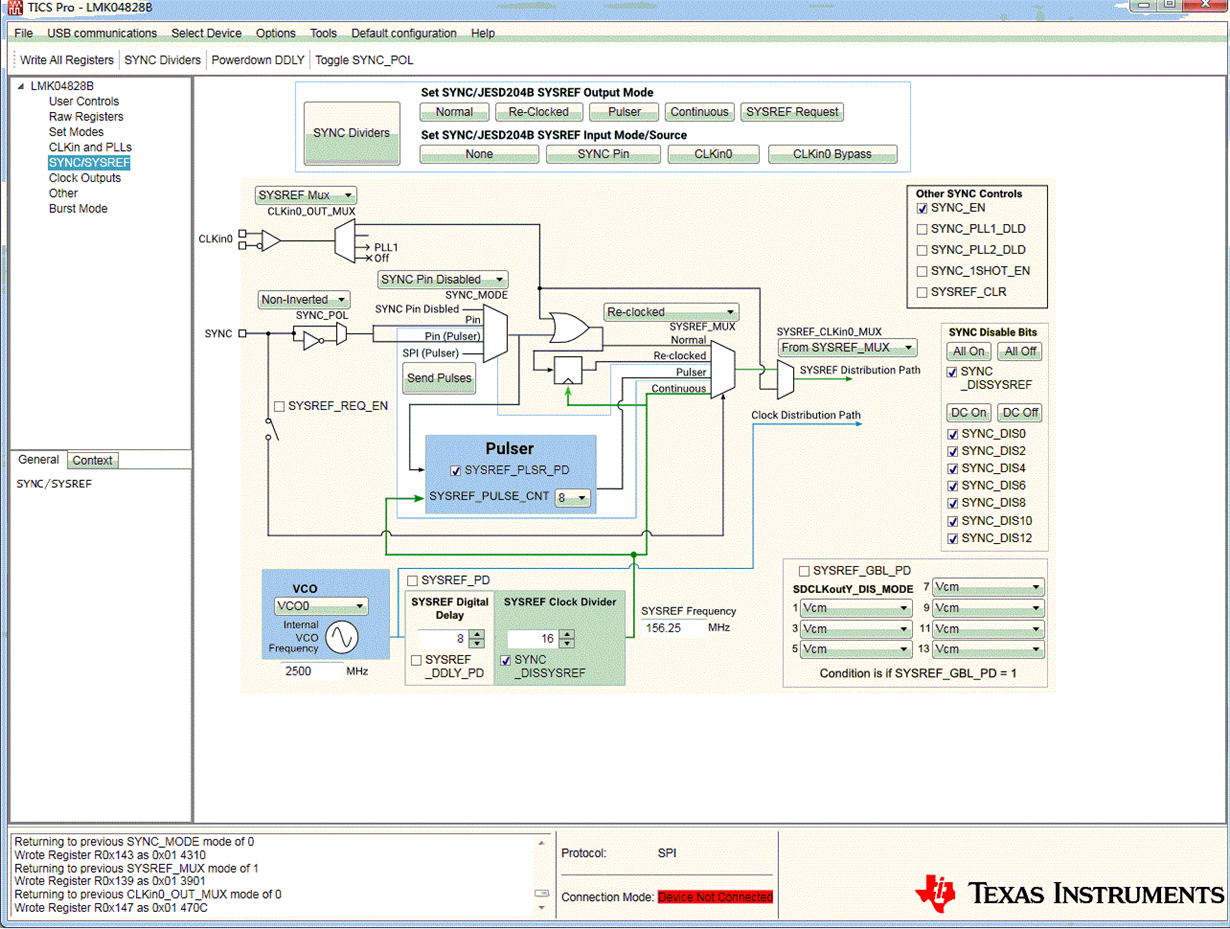

我使用时钟配置工具导出寄存器值,这是FPGA Finish LMK设置中的SPI Mater模块。

我错了哪里??