Other Parts Discussed in Thread: CDCE949

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:CDCE949 您好,

我想创建25 MHz PLL输出,我找到了两个PLL设置:

-输入时钟为27 MHz。

- Y7是我在Attache TI Clock Pro捕获文件中的目标PLL。

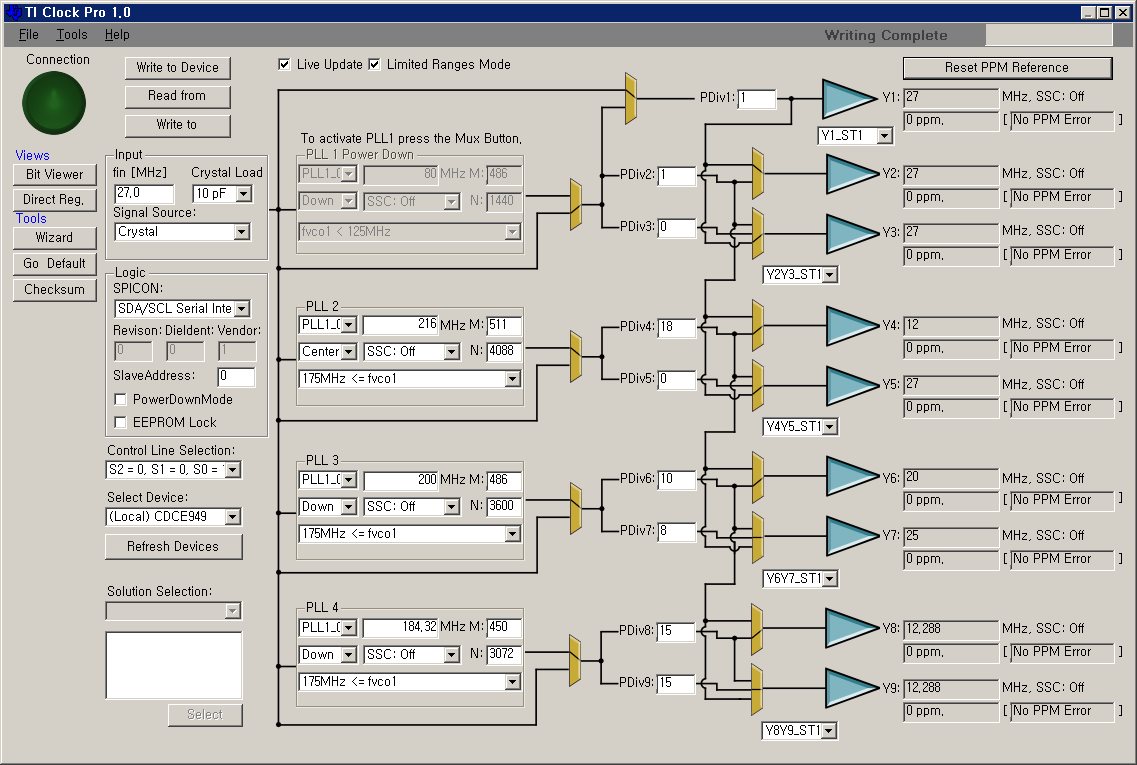

1. 第一个设置(2015_1223)1223)

M = 486

N = 3600

Pdiv = 8

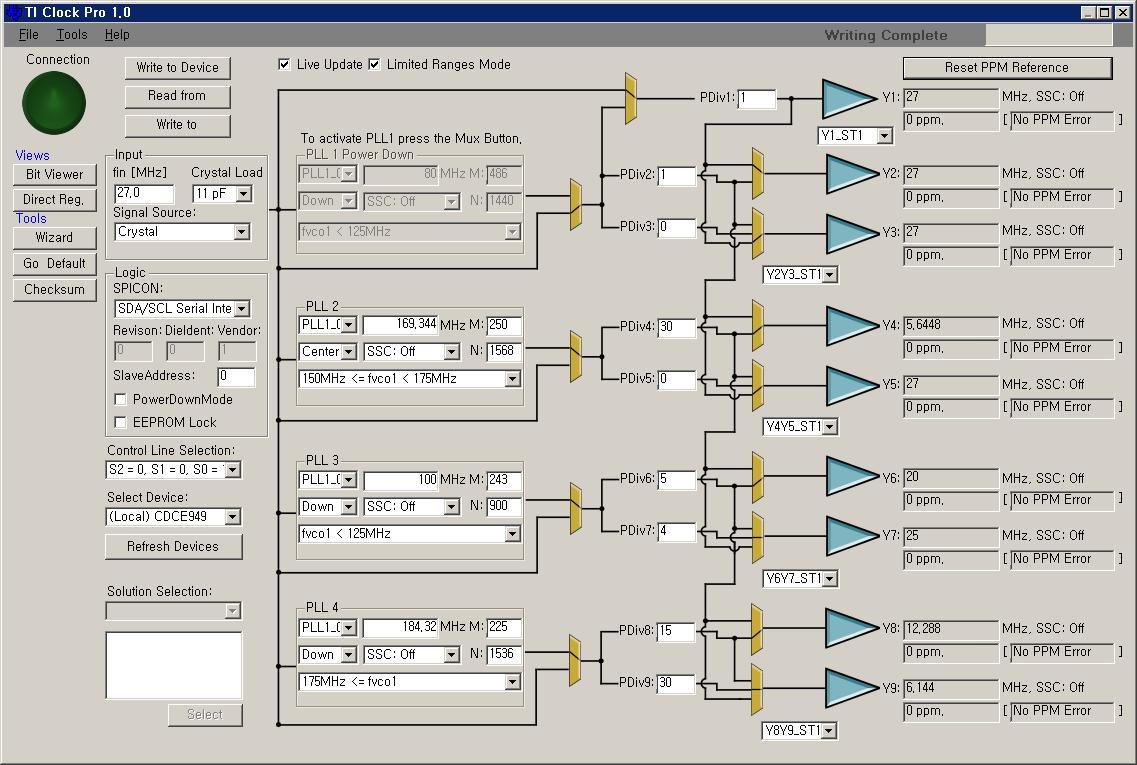

第二个设置(2017_0217)0217)

男=243

N = 900

Pdiv = 4

最终输出时钟均为25 MHz。

- Fout = Fin/Pdiv x N/M (CDCE949数据表第25页)

我的问题:

哪种设置在两种设置之间更好?

第一个是TI时钟专家向我展示的内容。

第二个是我改变了第一个,使M,N和Pdiv变小。

附加文件是 用于这两种设置的TI Clock Pro捕获文件。

谢谢。