Other Parts Discussed in Thread: CODELOADER

主题中讨论的其他部件:CODELOADER

两个从LMK(LMK_A和LMK_B)处于单循环SYSREF 0-Delay模式,SDCLKouts应在通电后与参考输入相位对齐,并具有同步脉冲,所有DCLK和SDCLK都应同步。

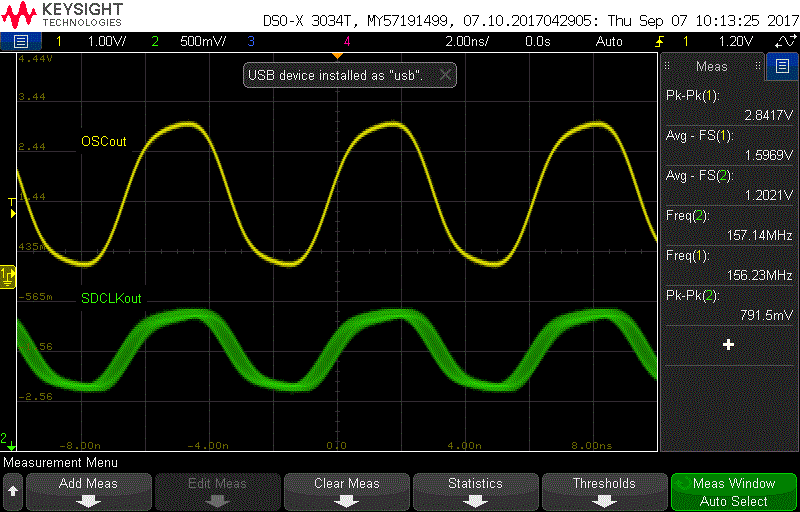

现在我可以看到两个从属LMK的OSCout是相位对齐和稳定的,从LMK_B的SDCLKout也是相位对齐OSCout ,这些都是预期的,

但OSCout A的相位与LMK_A的SDCLKout不一致?

锁定指示灯LED亮起,两个从LMK相同,这是否是相位检测器错误? 或者芯片损坏了??

必须在 SYSREF 0-Delay 模式中启用SYNC_DISSYSREF位,我是不是?

即使SYNC PIN已禁用,SYNC_DISSYSREF已启用,切换SYNC PIN仍可重置SDCLK的阶段,为什么??

谢谢