请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:CDCE706 尊敬的支持团队:

在客户的系统中,可能会有一些参考 CDCE706的运行clk,请帮助评估对706的影响,客户需要 决定是否使用它。

1.它是否会失去锁定?

2.如果是, 是否仍有输出?

3.如果仍有输出,相位噪音又如何? 我们是否有一些测试数据?

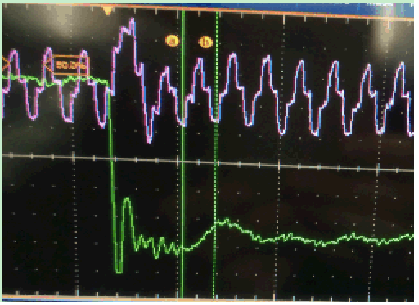

runt clk波形可能是:丢失多个周期, 更改占空比,更改振幅 等...如下所示,绿色曲线是runt clk,抖动约为2ns: