主题中讨论的其他部件: LMK0.0304万, LMK0.1万,

大家好,我很难为我的设计选择合适的拓扑。

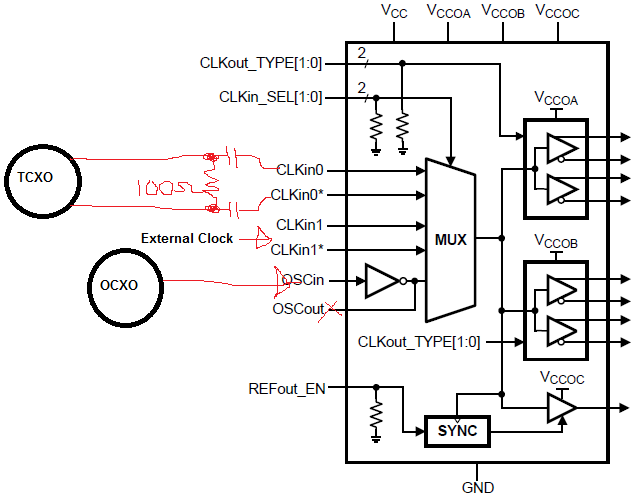

我有三个参考时钟,我想为我的PLL (LMX2594)参考时钟一次选择一个。

-一个时钟基准是PCB上的OCXO,用于低相位噪声

-一个时钟参考是PCB上的TCXO

-另一个是外部时钟。

问题是TCXO不能驱动50欧姆负载(至少是我搜索过的负载)。 如果您知道,请向我推荐一个)。 于是我开始搜索fanout缓冲区。 但是,它们需要像LMK0.0304万这样的高转换速率,我的OCXO和TCXO的输出转换速率大约为3V/5ns。

请问您能为我提供解决此问题的方法吗? 什么是具有最低附加抖动且需要更低输入转换速率的最佳缓冲区? 还是 有比使用扇出缓冲区更好的解决方案? LMK0.1万是我能找到的最好的一个。

我也找不到有关LMX2594参考时钟所需的最小转换速率的任何信息。