主题中讨论的其他部件: DAC38J84, DAC37J84

您好,

在阅读了几个数据表和应用程序说明后,我仍然有一些关于如何生成正确的SYSREF和同步信号的问题。

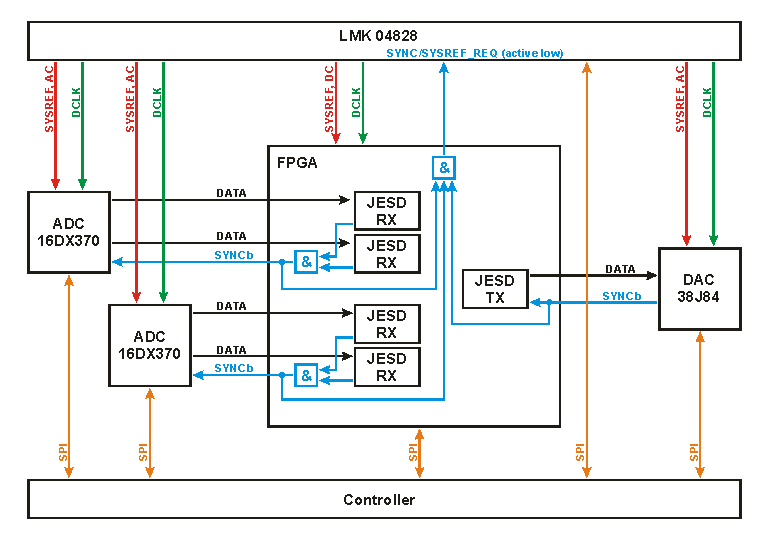

我们希望使用子类1来确定系统中ADC和DAC之间的确定性延迟:

(11月 20:编辑过的图像)

在LMK初始化过程中,内部分禾器通过切换同步极性寄存器位(SYNC_POL)进行同步。 随后,禁用分隔符同步(Sync_DISxx)。 现在,在设备时钟稳定后,我们初始化ADC,JESD IP核心和DAC。

通过将SYNCb线路拉低,每个JESD接收器都可以使相应的JESD发射器发送同步序列,但我们应该在何时以及如何请求LMK生成SYSREF脉冲?

例如,我们可以在SPI上触发SYSREF脉冲,这与我们在初始化和内部同步期间的方法相同。

我们甚至可以定期重复此操作,并检查设备是否重新同步。

另外,我们还可以将所有SYNCb输出(来自DAC和JESD RX IP核心)连接到通用SYNCb (至ADC,JESD TX IP核心和LMK)中,以便在同步请求时自动生成SYSREF。 但是在我看到的每一个图中,SYSREF都在SYNCb被拉低之前结束,所以我们可能需要将SYNCb延迟到ADC和JESD TX IP核心。

那么,是否有一些常见或首选的方法来触发SYSREF生成?

此外,我发现有几种SYSREF生成模式(一个脉冲,多个脉冲)和接受模式(所有脉冲,第一个脉冲,第二个脉冲,第一个脉冲之后的所有脉冲...),但我没有找到任何建议使用哪一个以及为什么。

此致,

Michael。