主题中讨论的其他部件:TLC555,

继续执行此开机自检中的故障诊断: https://e2e.ti.com/support/clocks/f/48/t/65.0131万。 通过降低输出电容以消除芯片加热,该接线柱中的问题得到了解决。

555计时器输出的占空比根据输出负载而变化。 在约72.5欧姆(测量值)的情况下,占空比为100 %。 当电阻为120欧姆时,占空比降至~Ω 80 %。 我担心555计时器在之前的故障排除和操作中受到损坏,但我正在寻找任何其他解释,说明为什么负载会影响 芯片的占空比,而不是损坏。

探测了触发器和阈值引脚后,这些引脚处的电压没有上升超过~6V,并且控制电压为~6.5V ->,因此电压阈值正常,但触发器/阈值的充电未超过触发器触发所需的6.6V。

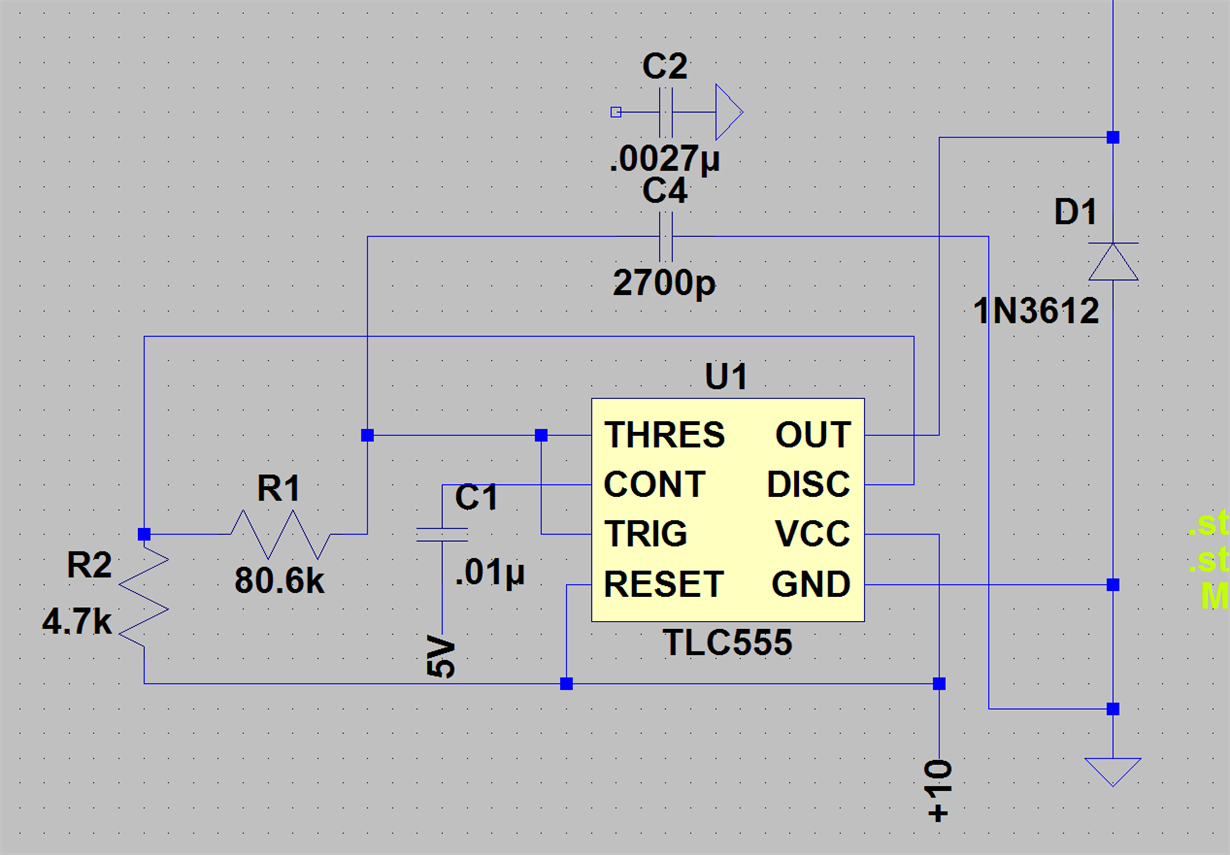

我对LTSpice原理图表示歉意,但我仍在学习TI-Tina,现在我的学习速度更快了。 尽管公认唯一可用的仿真芯片是TLC555,而不是LM555,但仿真不会显示不同载荷的问题或频率偏移。

我将继续在实验室中对问题进行故障排除,并尝试进行芯片交换,以查看操作是否发生变化。