Other Parts Discussed in Thread: TLC551

您好,

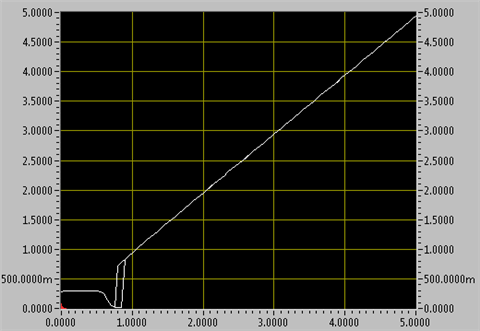

在TLC551上,当Trig引脚较低且Threshh引脚较高时,输出显示为LOW (低),但Trig应覆盖Threshh。 此问题通常在以Vdd低于1.3V的电压运行设备时发生,尽管有时电压较高。 所有测量均在Vdd初始通电时进行,转换速率约为1V/us;有时更快。 重置与Vdd绑定,无论是否操作控制引脚,此行为仍然存在。

在1.3V Vdd时,当Trig引脚和Therh引脚分别电容耦合到GND和Vdd (12nF两者)时,输出不理想地变为低电平。 如果仅将GND耦合盖更换为对地短路,则输出成功保持高电压。 但是,即使存在极短电压,当Vdd降至1.1V时,输出也会再次不受欢迎地变低。 已观察到EMI影响,但即使部分解决,这种现象仍然存在。 对于此应用,输出最初应为高,并保持高电压,至少保持高电压,直到触发电压超过触发电压。 触发阈值的引脚优先级是要保留的重要属性。 如果触发和引脚连接在一起,然后耦合到GND,则输出成功变为高电平。 但是,将它们捆绑在一起并不是理想的安排。

有什么想法,解决方案? 最好避免将任何部件放置在正极供油轨的主支路的路径中。

谢谢