专家,您好:

我正在使用LMK0.4828万的时钟设计工具进行PLL相位噪声模拟。 请您花些时间检查我的模拟过程中是否有任何错误吗?

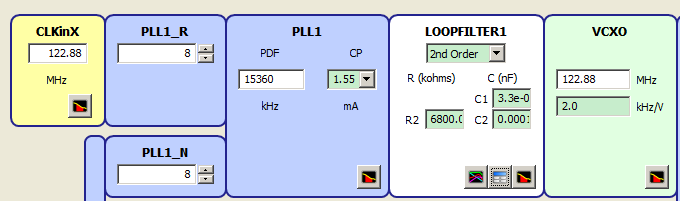

我通过在时钟设计工具中键入以下内容来模拟PLL1相位噪声曲线:

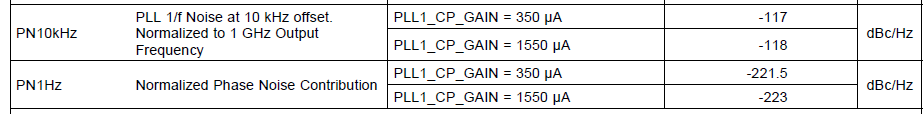

数据表显示PLL1的PN1Hz和PN10KHz如下所示:

我采用PLL1_CP_Gain = 1550uA,然后进行模拟。

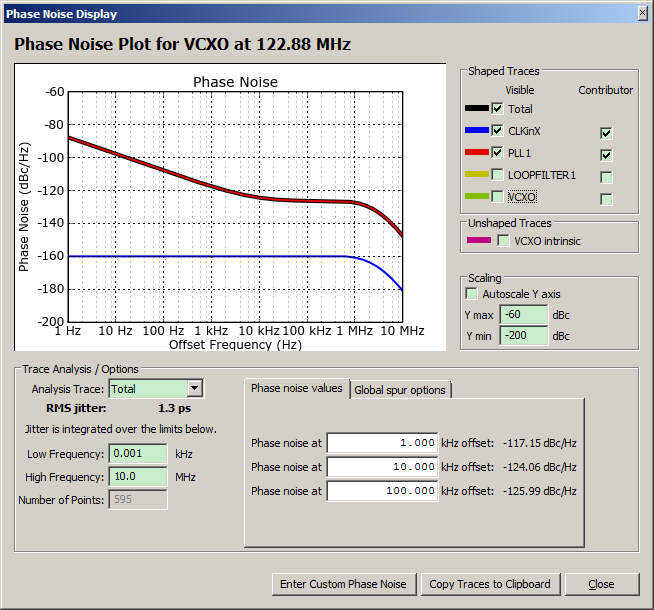

假设我的PLL1参考时钟为122.88MHz,PFD频率为15.36MHz,VCXO频率为122.88MHz。

- 我可以在PLL1输出时获得平坦噪声,如下所示:

Lpll_flat (f)= PN1HZ + 20log (N)+ 10log (fpdx)=-223 + 20*log (8)+ 10log (15.36MHz)=-133.07dBc/Hz

如果增加PFD频率,PLL1输出处的平坦噪声将提高10*logfpdx。

2.我还可以在PLL1输出的10kHz偏移处获得闪变噪声,如下所示:

Lpll_flicker(10kHz)= PN10KHz + 20log (输出/1GHz)+20*log (N)=-118 + 20*log (0.0.1536万)+ 20*log (8)=-136.21dBc/Hz

因为闪烁噪声 的斜率为-10dB/dec. 我可以在PLL1输出时获得以下频率范围内的闪烁噪声:

|

偏移(KHz) |

闪烁噪声@PLL1输出PN (dBc/Hz) |

|

0.01 |

-106.210.3759万 |

|

0.1 |

-116.210.3759万 |

|

1. |

-126.210.3759万 |

|

10. |

-136.210.3759万 |

|

100 |

-146.210.3759万 |

|

1000 |

-156.210.3759万 |

|

1万 |

-166.210.3759万 |

闪烁噪音保持恒定,与PFD频率无关。

3.因此,将闪变噪声和平坦噪声相加,我可以在VCXO输出处获得总PLL1噪声,如下所示:

|

偏移(KHz) |

PN (dBc/Hz) |

|

0.01 |

-106.20.1444万 |

|

0.1 |

-116.121.8725万 |

|

1. |

-125.397.3442万 |

|

10. |

-131.354.9013万 |

|

100 |

-132.868.3031万 |

|

1000 |

-133.53.2444万 |

|

1万 |

-133.72.1791万 |

以上是理论上我对 PLL1 VCXO输出的预期PLL1噪声影响的计算。

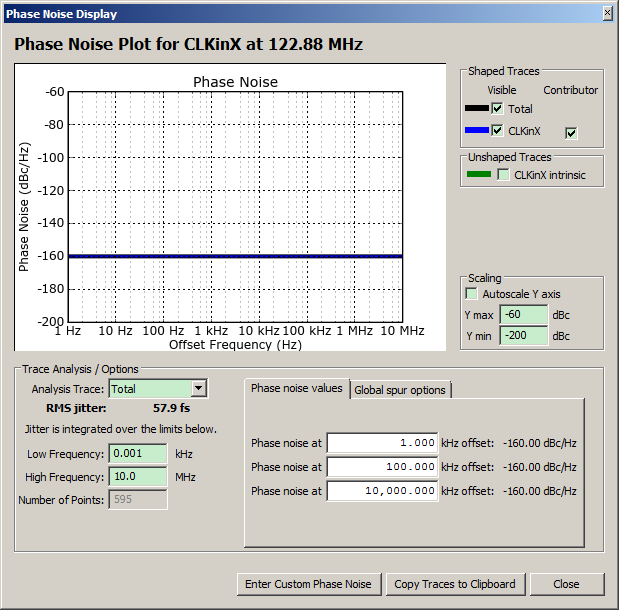

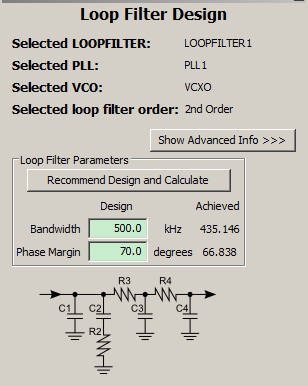

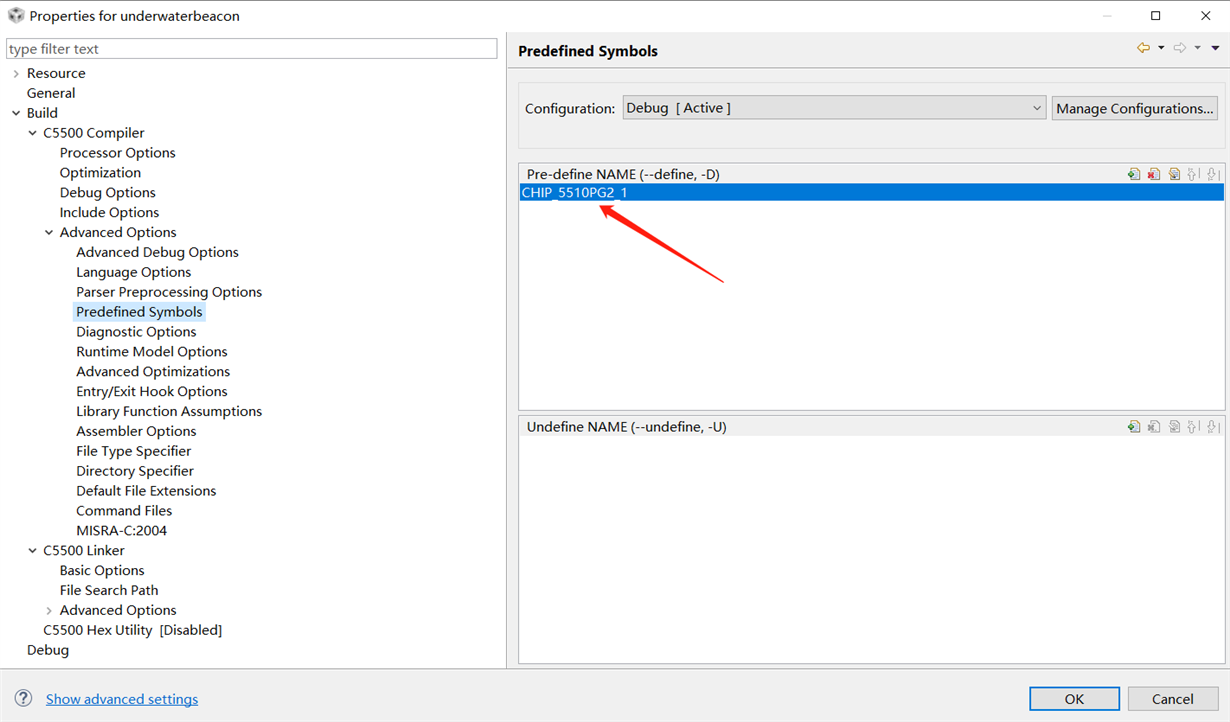

4.开始模拟

答 要排除参考相位噪声影响,我将参考相位噪声设置为-160dBc/Hz

B. 将PLL1回路带宽设置得足够大(~500kHz),以帮助我更 清楚地检查PLL1相位噪声

C. 另一方面,我禁用VCXO和回路滤波器的相位噪声贡献:

但是,我发现VCXO (PLL1输出)的模拟结果和计算结果之间存在巨大差距:

|

偏移(KHz) |

计算的PN (dBc/Hz) |

模拟PN (dBc/Hz) |

|

0.01 |

-106.20.1444万 |

|

|

0.1 |

-116.121.8725万 |

|

|

1. |

-125.397.3442万 |

-117.15 |

|

10. |

-131.354.9013万 |

-124.06 |

|

100 |

-132.868.3031万 |

125.99 |

|

1000 |

-133.53.2444万 |

|

|

1万 |

-133.72.1791万 |

|

我认为PLL1相位噪声(闪烁噪声和平坦噪声)可能有一些问题。 请帮我检查一下我的计算结果,看看是否有任何问题? 提前感谢您的参与。

谢谢

纱线