主题中讨论的其他部件: LMK0.4808万

您好:

我使用LMK0.4828万提供DAC采样时钟,外部VCO模式(1.728GHz原始时钟输入到CLKin1,并使DCLKOUT6输出1.728GHz时钟)。 未使用内部PLL)。

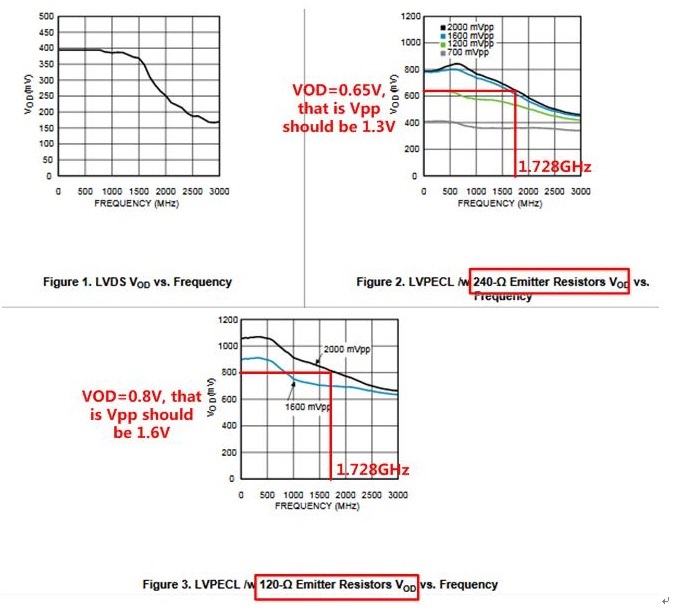

输出端口是DCLKOUT6,它被设置为LVPECL20的输出格式,输出P/N引脚被下拉至具有240欧姆电阻的GND,如下所示:

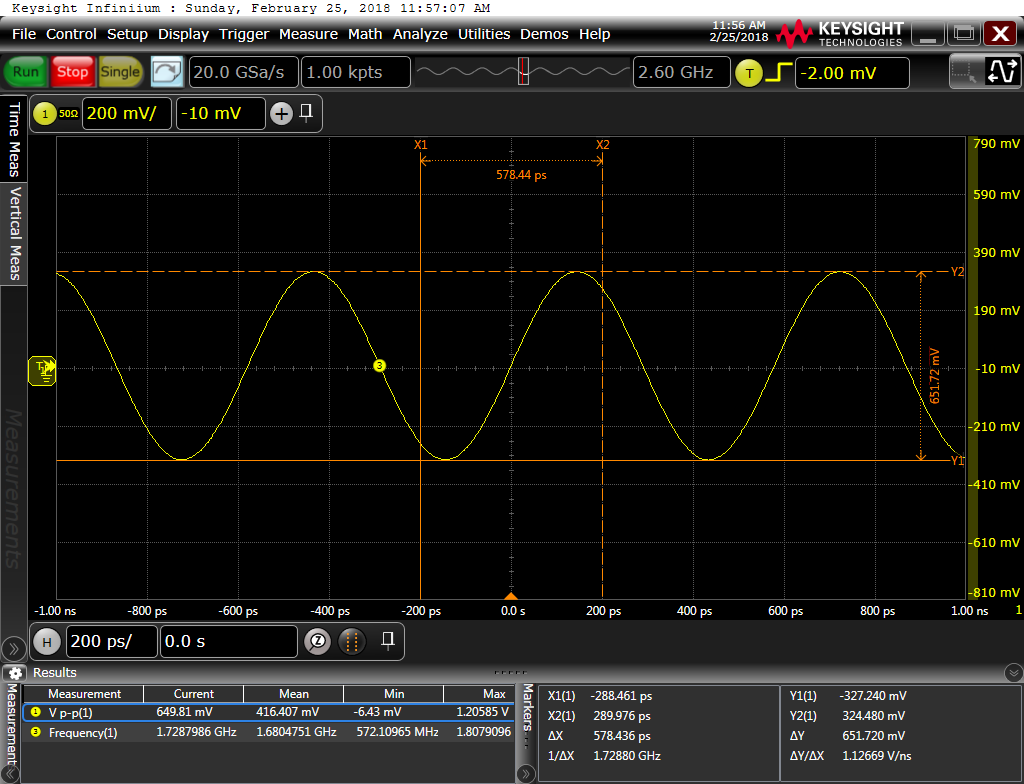

当使用差分探针测量DCLKOUT6的输出振幅时,结果Vpp大约为650mV,如下所示:

请注意:以上屏幕截图中的Vpp是使用差分探头测量的差分电压,而不是在两条差分信号线路之一上测量单端探头。

数据表显示,当输出格式设置为LVPECL20时,VOD为960mV,因此峰间电压差为2*960=1920mV。 (如数据表SNAS605AR所述:第27页-图9)。

因此,测得的650mV比所需的1920mV低得多,无法满足DAC采样时钟振幅的要求。

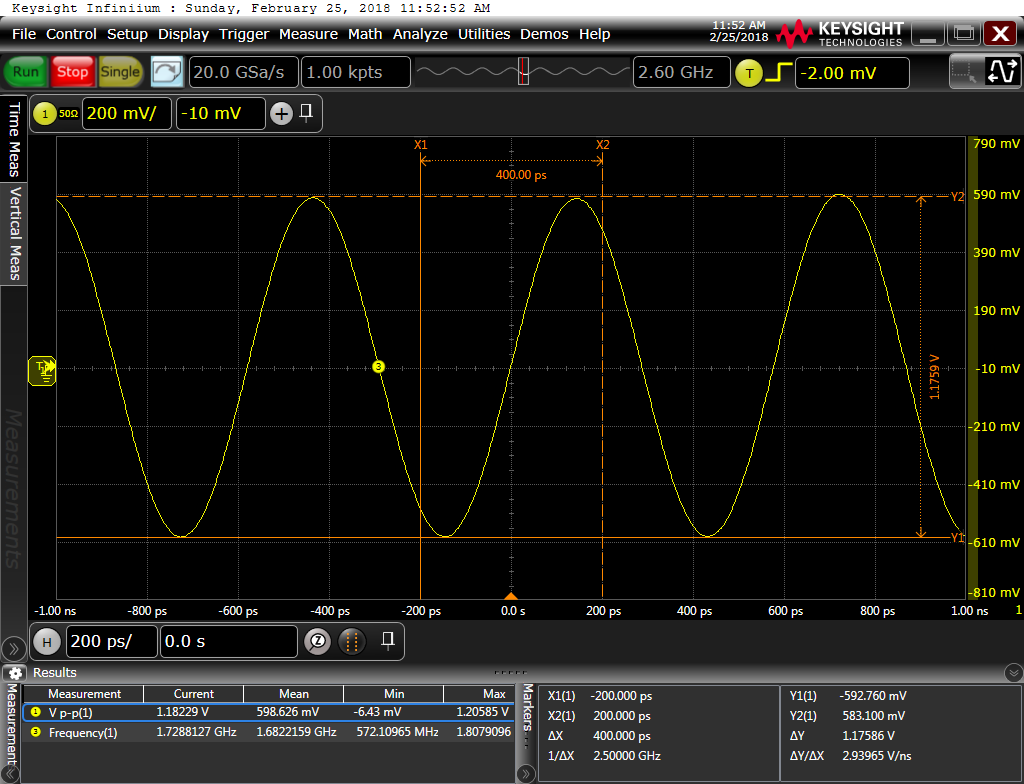

鉴于这种现象,我将 +和-线路的下拉电阻从240欧姆更改为50欧姆,然后输出Vpp增加到1180mV,但仍无法达到数据表额定1920mV,如下所示:

现在,您能找到问题所在吗?

谢谢!