您好,

我的客户希望按以下方式使用CDCM7005-SP。

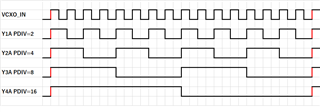

- VCXO_In --> PDIV=/2 --> Y0A (LVPECL)

- VCXO_In --> PDIV=/4--> Y1A (LVPECL)

- VCXO_In --> PDIV=/8 --> Y2A (LVPECL)

- VCXO_In --> PDIV=/16--> Y3A (LVPECL)

关于这种用法,他们有一些问题,如下所示。

问题1:

Y0A,Y1A,Y2A和Y3A上升边缘相位在16次VCXO_In循环后是否对齐,如下所示?

或者需要重置以对齐它们,如下所示?

问题2:

在数据表的图11中,LVPECL的最大tpd (lh),最大tpd (HL),最小tpd (lh)和最小tpd (HL)分别有多少?

问题3:

从取消RESET_断言到yna输出第一上升边缘的延迟有多大?

此致,

K.Hirano