Other Parts Discussed in Thread: LMX2594, LMK61E2

主题中讨论的其他部件:Tida-0.1021万, LMX2594, LMK0.0804万B, LMK61E2

您好,

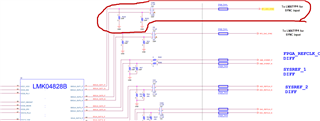

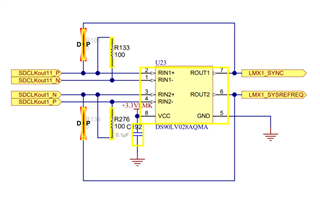

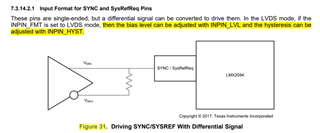

我想使用LMK0.4828万B+LMK2594同时2594同时向4个ADC提供器件时钟(10GHz)和sysref(4.882.8125万Mhz )时钟, 并实现 具有相位校准的多通道时钟解决方案。

4pc ADC的采样同步非常重要,因此应选择时钟方案以尽量减少采样偏差。 我 计划使用JESD204B子类1实现多芯片 同步,

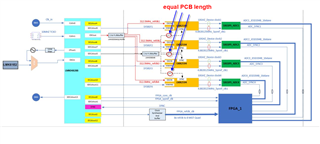

如下图所示,哪种时钟方案更好地实现 具有相位对齐的低相噪声DEVCLK生成和多通道时钟解决方案? 选项1还是选项2?

提前感谢!

选项1:

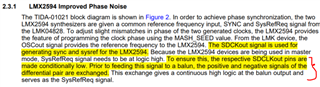

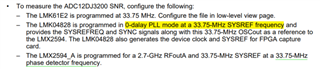

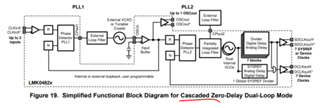

选项2:部分参考TIDA-0.1021万的设计