主题中讨论的其他部件:AFE7950, LMK0.4832万, AFE7950EVM, LMK0.4828万

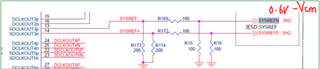

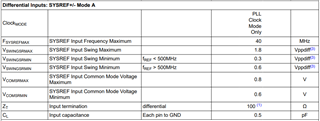

大家好,TI e2e,我希望能得到一些设计建议,用于涉及TI LMK0.4832万和 AFE7950部件的设计。 该设计涉及从LMK生成3.9.0625万 MHz LVDS时钟,该时钟馈入 AFE上的SYSREF输入。 我将在LMK上使用其中一个ODD CLKOUTX对。 我的问题涉及LVDS通用模式偏置,因为根据安全站点上的AFE79XX_Schema_layout_checklist,SYSREF需要从外部设置为0.6 V, 这是AFE数据表上的最小VCM,第19页(以下片段),最大VCM为0.8 V。VOD摆动通常为0.75 Vpp。

我在 每个SYSREF +/-线路上配置0.1 UF AC耦合,这将移除直流偏移并改变共模电压水平,但这可能不 是AFE SYSREF输入所期望的最佳方式,我确信其偏置功能。 是否可以为外部设置通用模式提供任何建议? 也许我需要一个直流回电路径的电阻器网络? 感谢你能抽出时间。