线程: LMK0.4906万中讨论的其他部件

您好,

我是否可以使用反馈时钟中0延迟模式顶部的数字延迟来获得与输入时钟相比的其他输出的相位提前?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我是否可以使用反馈时钟中0延迟模式顶部的数字延迟来获得与输入时钟相比的其他输出的相位提前?

您好,Joe,

当使用0延迟模式的反馈路径中存在延迟时,反馈路径时钟输出与CLKIN相位,并且根据反馈路径中的延迟,其他时钟输出之间可能存在相位差异。

如 数据表中的8.3 10部分所述,在0延迟模式下,最低频率时钟输出应用于反馈,以确保CLKIN与CLKout相位关系固定。

谢谢!

此致,

Ajeet Pal

您好,Ajeet Pal,

我现在没有要测试的实际硬件,但我在这里附加了.TCS配置文件。

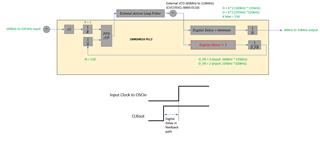

为了简化,这是我所期望的:

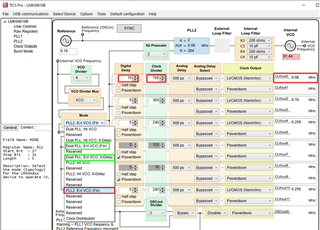

但是,我对如何在TIC PRO中正确配置外部VCO模式有疑问。

我注意到有两种模式可供选择,用于具有外部VCO的双PLL,它们是非延迟和零延迟。

对于带有外部VCO的单个PLL2,只有1个选项。 这是否意味着它必须是内部零延迟模式?

CLKOutx始终根据TIC PRO中的内部VCO进行反射,我看不到外部VCO的频率输入框。

这是否因为外部VCO不像内部VCO那样进行校准?

您好,Joe,

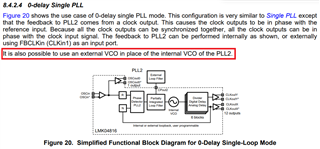

根据8.4 数据表中的PLL.VCO部分,也可以使用带有外部2.4 的单一PLL 0延迟模式,但无论如何 ,该选项 未显示在TIC Pro中。

正确,TIC Pro仅反映内部VCO设置,并且需要在其他寄存器上调整外部VCO。

与您一样,这似乎是正确的,但您可能需要根据0延迟模式下的外部VCO频率手动写入PLL2_N (N -反馈分频器)和PLL2_P (预N分频器)。

关于使用通道分配器和Keep N -->1为0-Delay提供反馈除法的查询,不可能,因为PLL2_P分配器具有最小除法值2,并且会出现在反馈路径中。

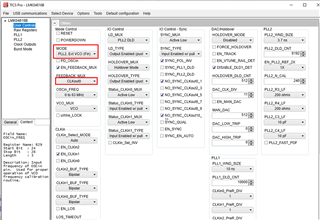

同步 操作和 NO_SYNC_CLKoutX_Y位设置为0后,反馈路径中的数字延迟也将被考虑。 按照数据表中的8.6 .3.4 3部分进行操作。

我建议订购EVM,并可以尝试使用您所需的频率。

谢谢!

此致,

Ajeet Pal

您好,Ajeet Pal,

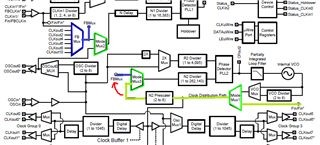

我认为,将模式设置为"PLL2,外部VCO"只会打开绿色路径。

通过启用反馈mux将只打开FB Mux (蓝色)。

可能仍需要某种"模式"设置来将模式Mux3从内部路径切换为反馈mux路径(红色箭头)?

很遗憾,我仍在等待完整的硬件来验证这一点。

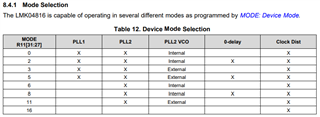

您是否可以确认LMK0.4816万能够实现"PLL2,带0-Delay的外部VCO",或者软件不支持此模式,因为它未在模式表39中列出?

您好,Joe,

TI尚未在0延迟单PLL模式下测试外部VCO,我也没有使用板载外部VCO的硬件进行验证。

即使数据表 也不会显示具有相同配置的任何模式。

将模式从"PLL2,Int VCO,0-Delay"更改为"PLL2,Ext VCO"和0- Delay"时;模式Mux 3不清晰,这可能是未定义Ext VCO 0-Delay"模式的原因。

由于未定义,TI不建议使用此配置。

我正在从设计方面检查此模式的可能性,并将很快更新您的信息。

谢谢!

此致,

Ajeet Pal

您好,Joe,

很抱歉回复延迟。

LMK0.4816万可以通过选择 模式Mux 13 (R11[31:27]--> x0D)并使用FBmux选择正确的反馈时钟来支持单PLL2,EXT VCO 0-延迟模式。

在0延迟操作中,可以根据时钟分频器获取N-div值。

此模式配置在设备中,但未在数据表中验证/披露。 因此,我们建议您从您的端确认

谢谢!

此致,

Ajeet Pal

您好,Ajeet:

最后,我设法使用实际评估板测试0x0D模式(使用外部VCO进行修改)。

但是,我与同步输出混淆了。

我希望所有输出在锁定和同步后都在上升沿同步(默认情况下所有CLLout的数字延迟= 5)。

下面是我的设置:

外部VCO,带0延迟,CLKout 0作为反馈时钟

输入OCSiin:160 kHz

输入乘数:1.

R计数器:2.

FPD:80kHz

N计数器:1.

反馈时钟分频器:768 (CLKout 0:80kHz)

VCO:61.44MHz

输出被锁定,但同步在下降边缘,而不是上升边缘。

我在这里遗漏了什么吗?