尊敬的 Derek:

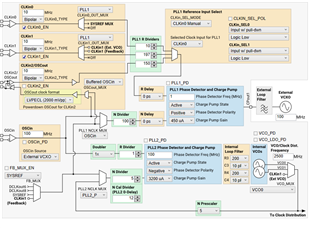

我们在定制板上使用 LMK04828芯片并生成256MHz 时钟和4MHz SYSREF、我们看到 DAC 输出上出现25KHz 杂散。

我想在两种情况下介绍我的建议

案例1:

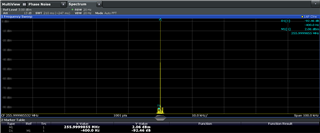

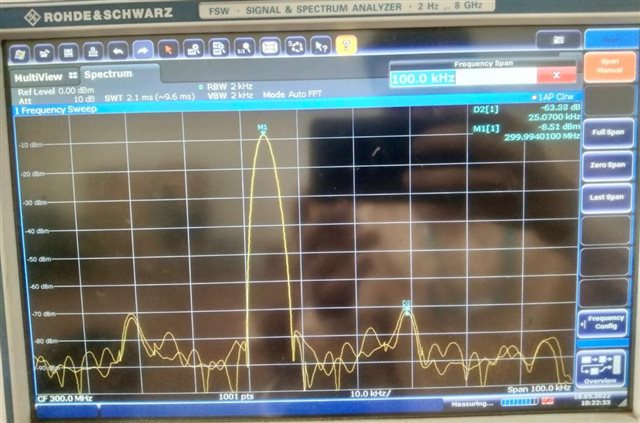

我们有一个评估板、它使用 LMKIN0 =10MHz 的 LMK 芯片和 DAC、外部 VCXO 为160MHz、生成256MHz 时钟和

4MHz SYSREF。我们将从电路板生成非常干净且没有任何杂散的 DAC 输出。我已附加其配置文件。

案例2:

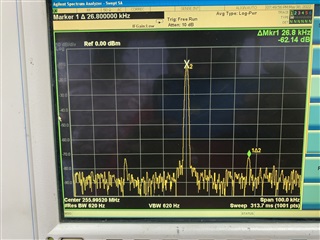

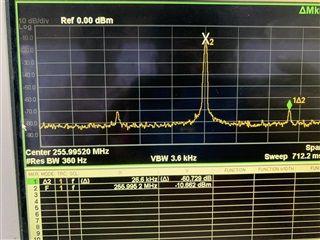

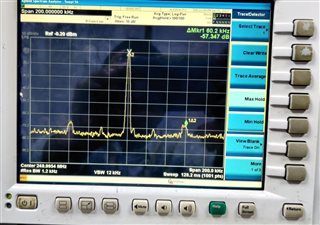

在我们具有 LMK04828芯片并生成256MHz 时钟和4MHz SYSREF 的定制板上、我们发现除了中心之外、还有两个频率为25KHz 的杂散

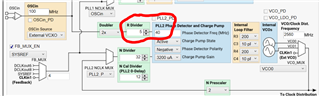

我们认为它是由两个 VCO (2560mH)的组合产生的  e2e.ti.com/.../eval_5F00_board_5F00_configuration.txte2e.ti.com/.../VCO2560MHz_5F00_configuration.txte2e.ti.com/.../VCO3072MHz_5F00_configuration.txtz)和外部 VCXO (100MHz)、因为

e2e.ti.com/.../eval_5F00_board_5F00_configuration.txte2e.ti.com/.../VCO2560MHz_5F00_configuration.txte2e.ti.com/.../VCO3072MHz_5F00_configuration.txtz)和外部 VCXO (100MHz)、因为

我们将 VCO 更改为3072、我们不会看到25KHz 的杂散、但由于选择的 VCO 频率在 VCO 范围的边界、因此我们将得到其他频率杂散、本底噪声也会增加。

我们尝试将100MHz 的外部 VCXO 更改为160MHz、但在单环路 PLL2模式下、我们仍然会发现25kHz 杂散。

我已附上2560MHz VCO 和3072MHz VCO 的配置文件。

是否有任何方法可以降低这些杂散的水平?

谢谢你