主题中讨论的其他器件: CDCE6214

您好专家、

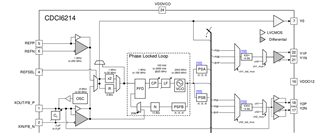

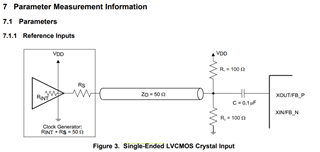

我的客户希望在 CDCI6214上使用单端 LVCMOS 50MHz 时钟作为参考时钟。

有关参考文献的问题有2个 CLK。

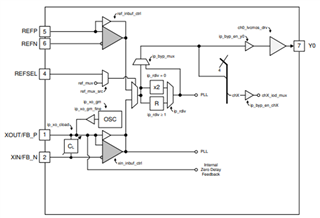

1.将 CLK 输入设置为 REFP/N 时:

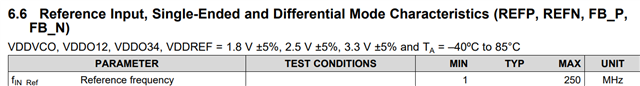

REFP/N 是差分引脚、如何处理外部单端输入时钟?

它是否可以使用平衡-非平衡变压器来传输单端到差分信号?

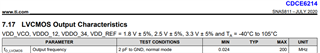

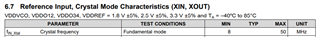

2. 我还注意到 XOUT 可以使用单端 LVCMOS 输入。

CLK 最大值 =50MHz 时、它将非常接近数据表中的极限频率、您建议这样做吗?

3. 在这种情况下,您能给我们一些建议吗?

谢谢。