你好

我设计了 LMK04803板 和 TICS Pro 生成的寄存器。 PLL2未锁定。

输入时钟频率:40MHz,COMS;

输出时钟频率:80MHz、LVDS、x10;

MODE:PLl2,INT VCO、0延迟。

TICS Pro 生成的 hex 文件:

e2e.ti.com/.../HexRegisterValues_2D00_E.txt

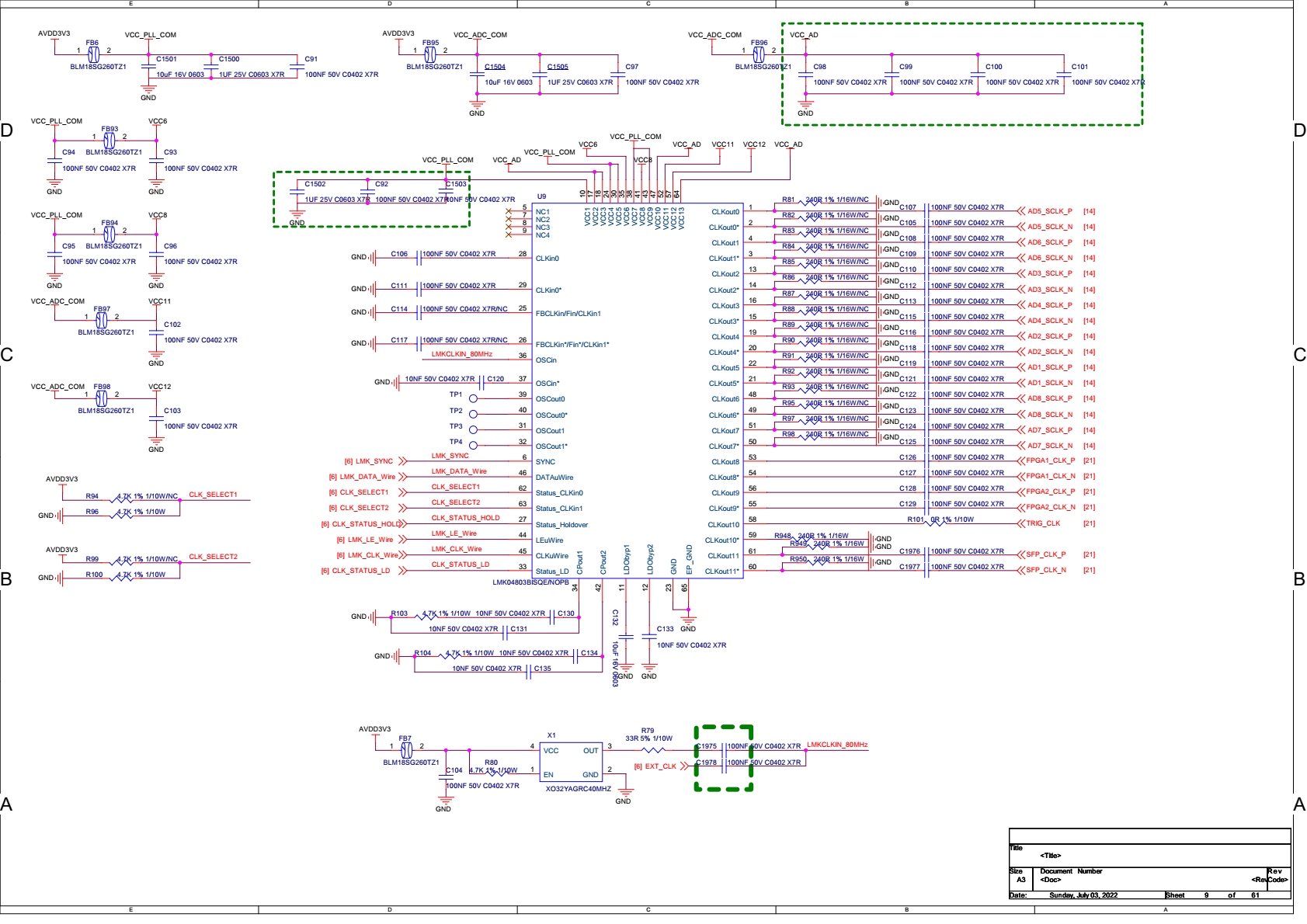

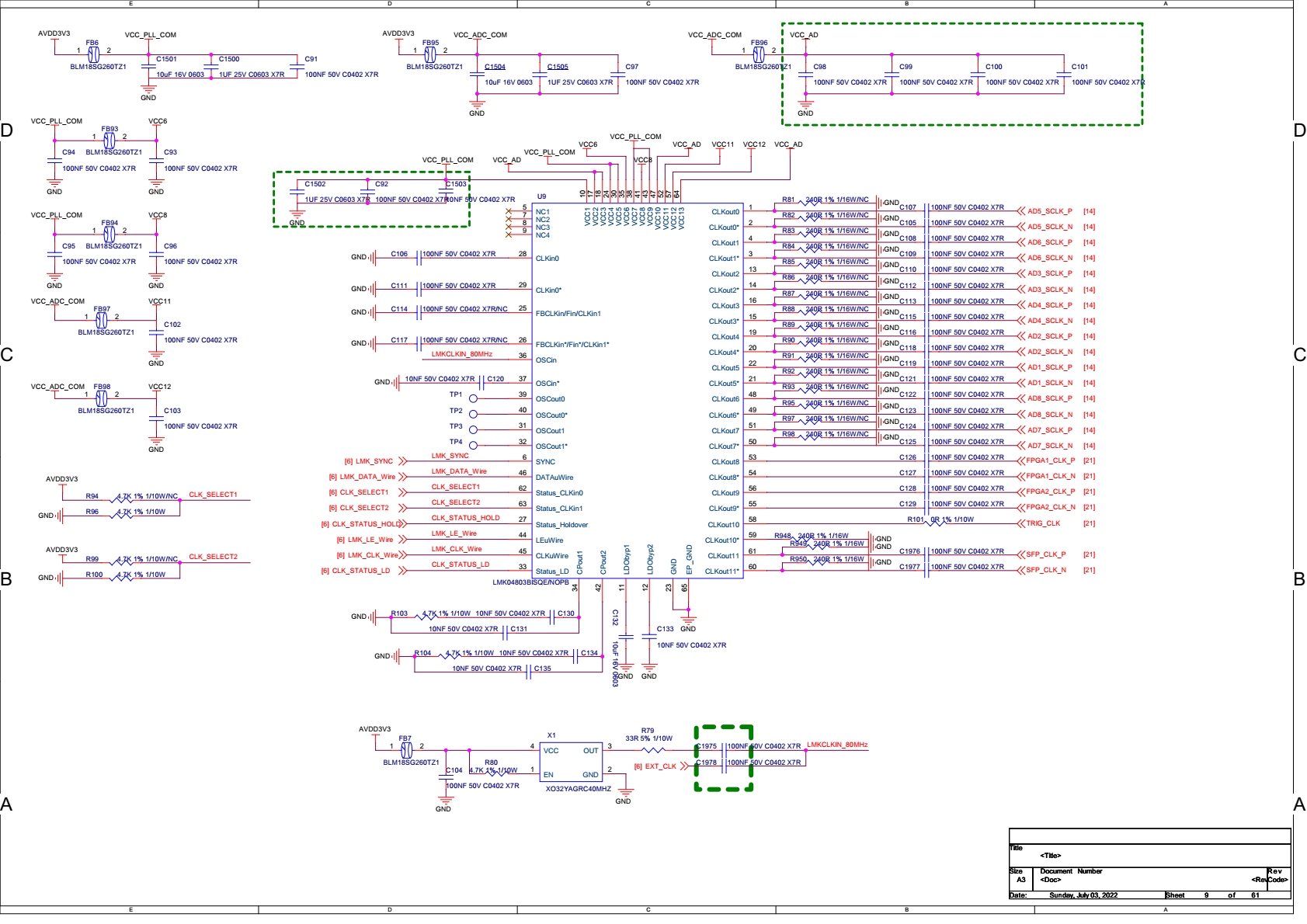

原理图:

VCC_PLL_COM 的噪声 为30~40mVpp。支持的分频器读数正常。

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好

我设计了 LMK04803板 和 TICS Pro 生成的寄存器。 PLL2未锁定。

输入时钟频率:40MHz,COMS;

输出时钟频率:80MHz、LVDS、x10;

MODE:PLl2,INT VCO、0延迟。

TICS Pro 生成的 hex 文件:

e2e.ti.com/.../HexRegisterValues_2D00_E.txt

原理图:

VCC_PLL_COM 的噪声 为30~40mVpp。支持的分频器读数正常。

谢谢你。

您好!

如果您要从 sig gen 馈送外部单端40MHz、则需要在 OSCin 输入引脚(C1978)处提供50ohm 终端。

另请尝试不使用 VCO 分压器、看看性能。 随附的配置文件 FYR。

谢谢!

此致、

Ajeet Pal

我觉得参数可能有问题。 TICS Pro 生成的一些参数与 数据表中所述的不同。

en_feedback_MUX(R10-11)=1

Feedback _MUX(R10-7:5)=0

CLKoutX_Y_DIV(R0-15-5)=24

PLL2_N (R30-22:5)=6

PLL2 PDF (N)= VCO 频率/CLKoutX_Y_DIV / PLL2_N=1920/24/6=13.333

PLL2 PDF (R) =40M*2/1=80

这两者的自由是不同的。

谢谢!