主题中讨论的其他器件:LMK04828

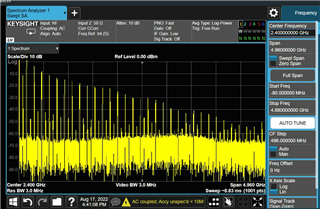

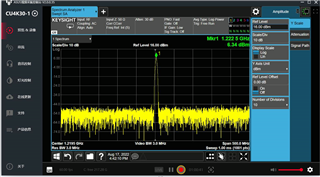

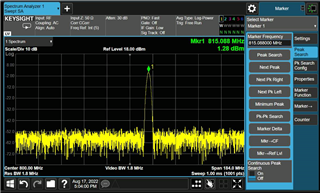

移除 C4、R3_AB1和 R18器件并连接 R1以确保电路板时钟完全断电后,我将 OSCin*和 CLKin1*连接到同一信号源输出的两个100M 3DBM 信号(已通过频谱分析仪校准) 并通过 TICS PRO 进行在线配置。 目标需要2.4G 频率点的输出、但观察频谱分析仪、没有任何频率就无法获得 VCO0的频率点。 在频分频后、输出时钟将被偏移。 如果配置了1200M、将获得1222M、如果配置了800M、将获得815M。 我们是否需要移除时钟 CVHD-950-122.88? 或者是否有另一种思考方式? 输出端子的 DCLKout0。