大家好、TI 团队。

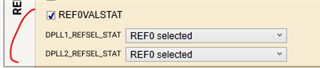

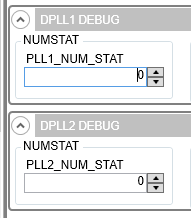

我对锁相有几个问题。 DPLL2的4个输出具有带输入时钟(REF0)的固定相位、但来自 DPLL1的其他4个输出没有。 到目前为止、我们 已确认四个状态(检测到 PLL1锁定、 检测到 PLL2锁定、 DPLL1失锁和 DPLL2失锁)均正常。

我尝试更改 DPLL 锁相 阈值(使用寄存器 R359和 R360)。 但它仍然无法解决问题。

问题是:

如何 锁定 DPLL1的相位?

2、为什么两个 DPLL 不同?

附件是我的 TICS Pro 配置文件。 谢谢、期待您的回复。