您好、先生、

我想确认如何为 LMK04832NKDR 使用 SYNC 引脚(在分配模式下操作)。

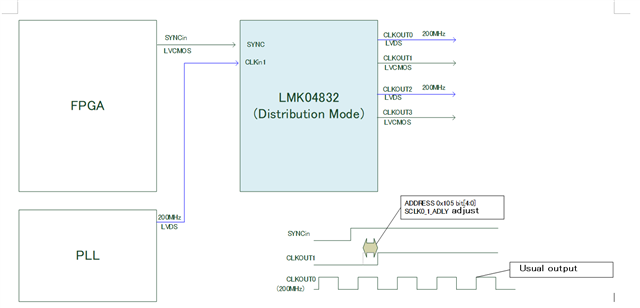

请查找附件。

FPGA→连接到 LMK04832 SYNC 引脚

PLL→输入200MHz LVDS 至 CLKin1

能否按上述方式调整 FPGA 的输出延迟?

谢谢。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、FRANK1、

要清楚一点、您需要:

您还可以在分配模式下使用 SCLKx_y_DDLY 和 SCLKx_y_HS;DDLY 时钟将只是200MHz 信号。 您好像在尝试调节 SYNC 信号、以便 CLKout1上升沿与 CLKout0下降沿等时。 如果您可以等待从 SYNC 信号到 CLKout0信号的几个200MHz 周期(因为 SCLKx_y_DDLY 必须设置为非旁路值)、SCLKx_y_HS 会将 CLKout1输出偏移到 CLKout0的恰好下降沿。

此致、

Derek Payne

尊敬的 Derek:

感谢您的回答。

我想确认更多信息。

-clkout1输出(检查 agian)

FPGA μ,的 SYNCpin 输入和输出

它可以根据我附加的图获得 clklout1的输出、对吧?

-SCLKx_y_HS

在数据表页55中注册0x104等。

"1:调整器件 SYSREF 相位-0.5时钟分配路径周期。"

这意味着漂移0.5个时钟(2.5ns (200MHz))、对吧?

-SCLKx_y_DDLY

表3。 数据表第35页中的 DCLK_DIV_ADJUST。

这些值意味着什么?

谢谢。

FRANK1、

[引用 userid="423996" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum 1059117/lmk04832-sync-pine-issue/3919312#3919312"]-clkout1输出(检查 agian)正确

[引用 userid="423996" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum 1059117/lmk04832-sync-pine-issue/3919312#3919312"]-SCLKx_y_HS正确

[引用 userid="423996" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum 1059117/lmk04832-sync-pine-issue/3919312#3919312"]-SCLKx_y_DDLY从 LMK04832中的 SYNC 信号取消置位(分频器复位条件清零)到数字延迟计数器开始计数之间有一定的时间间隔。 该时间因使用的分频值而异、因此建议使用 DCLK_DIV_ADJUST 值、以帮助简化时钟上的边沿与不同分频值的对齐。 对于1分频情况、DCLK_DIV_ADJUST 并不重要、因为数字延迟不能改变1分频的相位(半步长除外)。 在1分频情况下、可以忽略 DCLK_DIV_ADJUST 表。

此致、

Derek Payne