请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK03328 Helllo E2E、

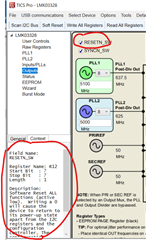

PLL 在上电时运行自动 VCO 校准需要应用哪些术语?

我之所以提出这一要求,是因为我们目前所做的是将 PLL 刻录到其内部 EEPROM 中,并且每次加电时 PLL 的值都从 EEPROM 中持续加载。

PLL 为 FPGA 提供参考时钟。

加电后、当从 EEPROM 加载 PLL 参数时、一切正常。

当我们尝试更改 PLL 输出分频器时(当然也是更改 FPGA 上的参数以适应新时钟),它不起作用。

我们在上电后、更改输出分频器之前添加 VCO 校准、然后系统开始工作。

您能解释一下在我们进行 VCO 校准时还做了哪些其他工作吗?

谢谢!

Russell