主题中讨论的其他器件: LMK05318、 LMK03318

您好!

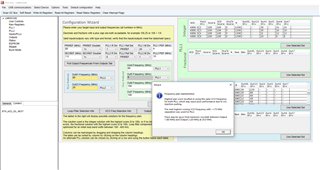

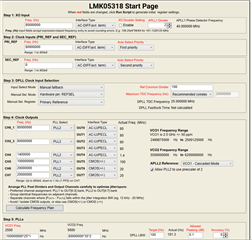

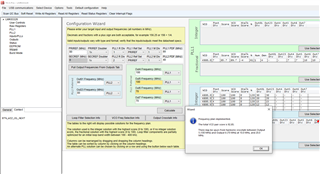

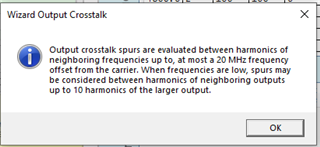

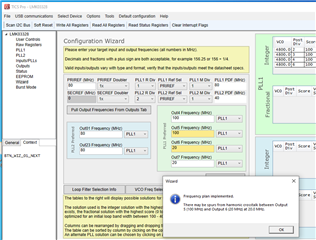

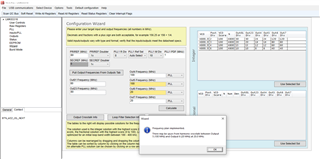

当我使用 TICS Pro 使 LMK03328生成2通道100Mhz、3通道80MHz 和2通道20Mhz 时、无论输出配置如何、我始终会在输出通道之间收到串扰警告。 但当我使用 LMK05318时、没有此类警告消息。 LMK05318是否有相同的问题? 或者、它有相同的问题、但软件中未显示。

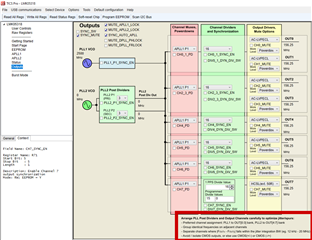

为了实现低抖动、是否可以在一个 PLL 中生成不同的时钟? 或者、最好在一个 PLL 中保持相同的时钟频率以减少串扰。

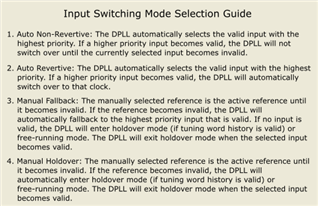

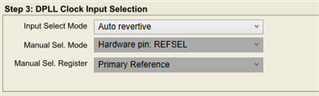

另一个问题是、我以前认为 LMK05318 XO 输入只接受振荡器。 但今天、我发现 XO 输入也接受来自其他驱动器的时钟。 这是否意味着我可以将 LMK03328输出连接到 LMK05318 XO 输入? 我需要 LMK03328、因为我需要基准时钟自动开关功能和 PLL 来锁定相位。 对于自动切换和 PLL、是否有任何切换具有相同的功能?

此致、

舒