您好、TI 论坛、

VCO 相位同步功能是否应增加相位检测器杂散? 我在1785MHz 下生成载波、其中通道分频 器= 6且包括分频器= 1、从而获得出色的噪声和杂散性能。 /- 40MHz 时的 FPD 杂散约为-90dBc。 当我选中 VCO_PHASE_SYNC 框时、IncludedDewide 会按预期变为6、并且 FPD 杂散会增加 约20dB。 可以避免这种情况吗? 帮助!

此致、

Mike Biggs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 论坛、

VCO 相位同步功能是否应增加相位检测器杂散? 我在1785MHz 下生成载波、其中通道分频 器= 6且包括分频器= 1、从而获得出色的噪声和杂散性能。 /- 40MHz 时的 FPD 杂散约为-90dBc。 当我选中 VCO_PHASE_SYNC 框时、IncludedDewide 会按预期变为6、并且 FPD 杂散会增加 约20dB。 可以避免这种情况吗? 帮助!

此致、

Mike Biggs

尊敬的 Mike:

您能否共享您的设置中使用的.TCS 配置文件? 我可以快速检查我的设置并查看性能。

同时 、同步模式中有两个要点:

1) 1)如果您的频率为 1.785GHz、请选择两个输出以显示为通道分频器。 您的 PFD 杂散应该会下降。

2) 2)对于分频频率:您可以减少 PFD_DLY_SEL 以及 MASK_ORDER。 这将减少杂散。

谢谢!

此致、

Ajeet Pal

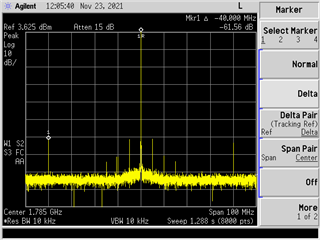

您好、Ajeet、附件 是.TCS 文件及其产生的频谱分析仪屏幕。 两个输出都设置为通道分频器。 使用 SYNC 的三次试验对应于一阶、二阶和三阶混频及其最佳 PFD_DLY_SEL。 如您所见、对于 所有混频设置、40MHz 杂散的影响最小。 此致 、Mike

e2e.ti.com/.../1785-nosync.tcse2e.ti.com/.../1785-sync-1st-order.tcse2e.ti.com/.../1785-sync-2nd-order.tcse2e.ti.com/.../1785-sync-3rd-order.tcs

您好、Michael、

我 可以在 LMX2594EVM 中看到与相位同步使能模式相同的性能。

环路 滤波器带宽和 PFD 频率越低、相位同步对杂散的影响就越大。

要改善 PFD 杂散、您需要优化固定低 PFD 频率(40MHz)下的环路滤波器带宽。 您可以使用 PLLatinum sim 工具 来优化环路滤波器带宽并更改板载组件。

没有启用相位同步的情况下的相位同步。

下图、具有优化的环路滤波器带宽(~90kHz)、支持相位同步(Mash Order - 3rd、PFD_DLY_SEL - 4)。

谢谢!

此致、

Ajeet Pal

因此、我听到您说、是的、相位同步确实会将 FPD 杂散提高20dB、而我只能做的就是改进环路滤波。

下一个问题、屏幕快照中+/- 2.5MHz 时的-45dBc 杂散来自哪里? 我看到在其他频率下、相位同步会出现类似的衰减。 随附的是我的1700.5MHz、+/- 1MHz 时为-33dBc 杂散。 不是很好!

Mike

您好、Michael、

正确的做法是、为了改善 FPD 杂散、应使用减小的环路滤波器带宽。

在之前的1785MHz 测试中、大杂散具有更高的混泥顺序(第3次)、可以通过减少混泥顺序来减少杂散。

关于 1700.5MHz 频率上+/-1MHz 偏移处的较高杂散、主要小数杂散在500kHz 偏移的倍数处出现。 也可以在 PLLatinum Sim 工具中观察到相同的情况、如下所示。

下面是 分数 N PLL 概念的链接 、用于了解各种杂散频率。

此致、

Ajeet Pal

您好、Michael、

关于相位同步+分数 PLL 模式下的杂散、在 LMX2594中、当启用相位同步时、根据设计、它会从通道分频器中添加额外的/4或/6分频器(包括分频)、并更新实际的 N 分频器。 在这种情况下、包含的分频器会影响杂散电平。 因此、会看到更高的振幅杂散。

在相位同步模式下无法减少这些杂散、但在降低电荷泵电流的同时、可以对其进行改进。 需要优化环路滤波器以实现相位噪声性能。 您可以使用 PLLatinum sim 工具 来优化环路滤波器带宽。

以下是~150kHz 带宽的更新环路滤波器组件值。 在电路板上应用此参数、并查看 FPD 杂散性能。

e2e.ti.com/.../40M_5F00_REF_5F00_1785M_5F00_Phase_5F00_Sync.sim

谢谢!

此致、

Ajeet Pal