主题中讨论的其他器件: CODELOADER

大家好、

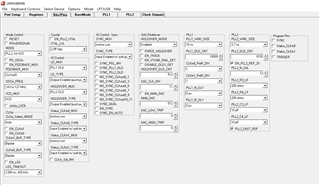

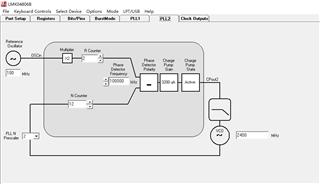

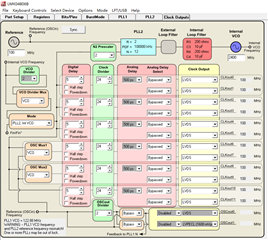

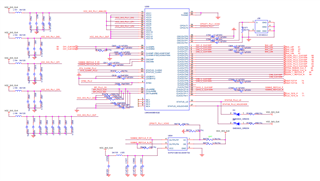

我的‘m 支持半导体测试仪项目。 客户希望通过 OSCin 将100MHz OSC 输入到 PLL2、对 PLL1断电、并将内部 VCO 设置为2.4G、然后将净100MHz CLKout 分成12个通道。 他们遇到了以下十六进制配置无法达到所需值的问题。 我不能接受现场支持、只能进行纸质审核。 您可以看看配置吗? 我看到的是、它们应该为 PLL2设置相位检测器极性为正。

谢谢。

e2e.ti.com/.../LMK04806_5F00_TI-FAE.txt