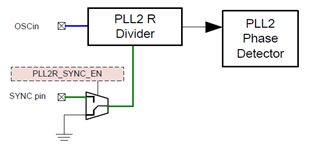

我们注意到 LMK04832时钟芯片中下面突出显示的语句、并想知道需要满足哪些设置和保持时间(特定值)、以及在下面段落的上下文中它们相对于哪个时钟? 我们没有看到同步行的计时表或图表。

请参阅数据表的第8.3.1.2节...

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Steve、

我们不确定保持时间、但设置时间不超过150ps。 实际上、CLKin0路径是唯一能够实际实现该设置时间的路径;SYNC 引脚上存在~3-5ns 的偏斜、因此通过 SYNC 引脚路径将最小设置时间视为5ns、在 CLKin0路径上为150ps。

我认为保持时间应该非常短、可能也是150ps。 这一切都发生在 CLKIN R 分频器上、该分频器在 CML 逻辑中实现、因此复位应该很快发生;与其他分频器不同、R 分频器(两个 PLL)上的最大频率受到严重限制、因此复位通常会非常快地发生。 在标记 TI 认为已解决之前、我将对此进行仔细检查;如果我听到不同的消息、我将在今天晚些时候发布更新。

此致、

Derek Payne

Steve、

我已经确认 CLKin0路径的保持时间应该非常短。 在实践中、我会说150ps、但我认为没有人会发送<300ps 脉冲来重置其 R 分频器。 一个实际建议是至少1/2 CLKIN 时钟周期。 SYNC 引脚 PLL1 R 复位也应如此、但由于传播延迟、设置时间为~3-5ns。

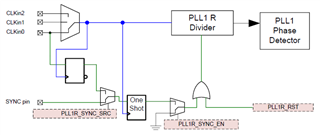

PLL2 R 分频器复位只能通过 SYNC 引脚进行、因此由 SYNC 引脚上的~3-5ns 传播延迟决定。 为了使该信号完全通过数字逻辑传播、最小脉冲宽度需要约为10ns。 由于 PLL2 R 分频器的复位是异步的、因此没有确切的保持时间限制、只要脉冲通过数字传播、整个 PLL2 R 分频器将很快复位(再次<150ps)。 理论上、您可以生成设置时间为~10ns 且几乎没有任何保持时间的10ns 脉冲、这就足够了。 但是、由于 SYNC 引脚上的数字路径具有较长的传播延迟、尤其是当 PLL2 R 分频器在大于100MHz 的信号上运行时、在 PLL2复位上获得正确的时序会有点棘手。 因此、应将 PLL2 R 分频器的最小脉冲宽度视为10ns、并将设置时间视为~3-5ns 之间的变量(假设最坏情况下为5ns)。

请注意、我们的大多数客户使用 PLL2 R 分频器作为1分频器、在这种情况下、无需重置 R 分频器。

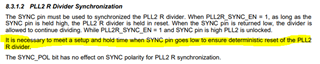

下面的一些图解释了 PLL1和 PLL2 R 分频器的 R 分频器同步路径。 我认为这些内容尚未纳入数据表、但在某个时候会包含这些内容。 PLL1 R 分频器复位路径在硬件引脚上至少有一个重定时级、软件复位是异步的;PLL2路径没有重定时器并且是完全异步的。

此致、

Derek Payne