主题中讨论的其他器件: LMX2820、 LMK04828

大家好、

我们在设计中使用 LMK04832、有关 Clkin0作为同步输入的问题我很少。

如果我们使用 Clkin0作为同步输入、它应该是单端还是差动。?

如果它可以是两种类型、那么它应该如何连接到 LMK04832 (如果它是单端或双电势)?

如果两种情况都需要交流耦合或端接、建议我这样做。

--

提前感谢、

Kiran

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们在设计中使用 LMK04832、有关 Clkin0作为同步输入的问题我很少。

如果我们使用 Clkin0作为同步输入、它应该是单端还是差动。?

如果它可以是两种类型、那么它应该如何连接到 LMK04832 (如果它是单端或双电势)?

如果两种情况都需要交流耦合或端接、建议我这样做。

--

提前感谢、

Kiran

您好、Ajeet、

感谢您的回复、

在我们的设计中、SYNC 将是 来自外部源的单端信号、我是否知道如何将该单端信号作为差分信号连接到 LMK04832?

我是否可以请求您就下面提到的几个问题提供反馈?

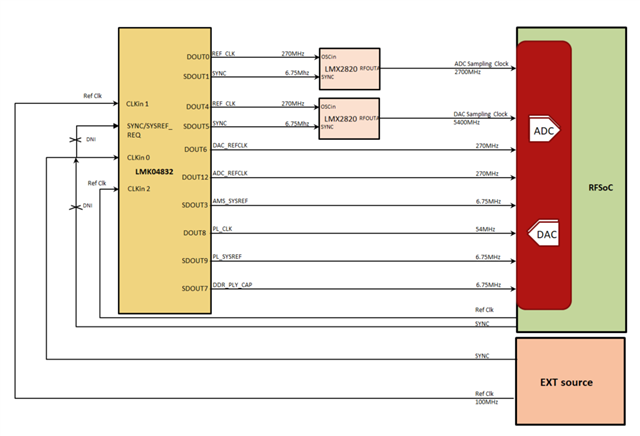

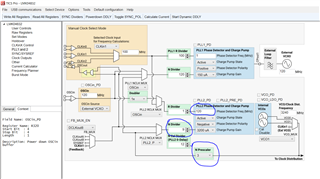

我们在设计中使用 LMK04832和 LMX2820来生成 ADC 和 DAC 采样时钟。 我们的时钟架构如下所示。

LMK 输入:

LMK04832默认具有外部源提供的100MHz 时钟输入1、OSCin 提供的100MHz VCXO 输入以及 Clockin0的同步信号输入。 (为 Clockin2和 SYNC/SYSREF_REQ 引脚提供可选的参考时钟和 SYNC)。

LMK 输出:

DCLKOUT0:270MHz (第一个 LMX2820的输入)

SDCLKOUT1:同步至第一个 LMX2820

DCLKOUT4: 270MHz (第二个 LMX2820的输入)

SDCLKOUT5: 同步到第二个 LMX2820

SDCLKOUT3: 6.75MHz AMS_SYSREF

DCLKOUT6: 270MHz DAC_REFCLK

SDCLKOUT7: 6.75Mhz DDR_PLY_CAP

DCLKOUT8:54MHz PL_CLK

SDCLKOUT9:6.75MHz PL_SYSREF

DCLKOUT12: 270MHz ADC_REFCLK

AMS_SYSREF、PL_CLK、PL_SYSREF 需要同步并相互对齐。

答:我们在双环路模式下使用 LMK04832、为了生成所需的输出、PLL2的 VCO1在3240MHz 频率下使用。 由于数据表指定了 VC01的最大频率为3255MHz、因此 VC01是否存在性能问题、因为我们在 VC01的上沿使用它?

PFA Ticspro 文件 FYR。

请验证 Ticspro 配置以了解我们的要求并提供建议。

b.由于 SYNC 是单端 信号、我知道如何将该单端信号作为差分信号连接到 LMK04832时钟输入0。 您能使用我们的原理图进行验证吗?

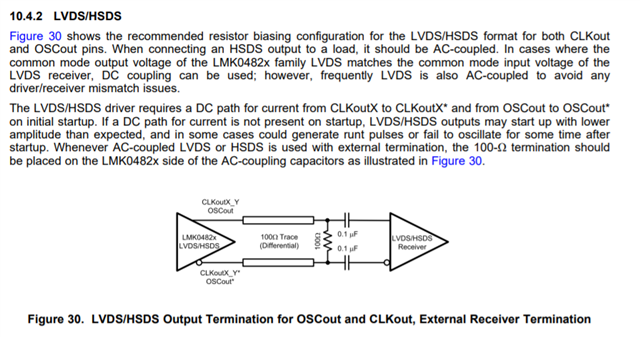

c.关于 LMK04828数据表中的时钟输出终端(由于 LMK04832和 LMK042828是引脚对引脚兼容的、因此我们为输出终端选择了 LMK04828)、在接收器处没有内部终端的时钟输出信号应按进行端接

我们的 DDR_PLY_CAP、PL_CLOCK、PL_SYSREF 没有内部终端、通常在将电容器耦合到负载引脚后需要100 Ω 外部终端、但 LMK04828数据表建议在将电容器耦合到 LMK 之前使用100E 终端。 接下来要关注哪个? 在我们的设计中、我们提供了可选的100E 耦合电容器、即 DNI。 您能否确认是否可以删除? (请参阅随附原理图的 pg5)。

d. PFA 原理图并验证 LMK、LMX 设计的时钟输入、输出及其终端、环路滤波器值和电源部分设计、为 LMK 和 LMX 供电并提供反馈。

e2e.ti.com/.../MS_5F00_TI_5F00_SCH_5F00_Review.pdf

e2e.ti.com/.../WBRFU_5F00_LMX_5F00_270MHz_5F00_5400MHz.tcs

e2e.ti.com/.../WBRFU_5F00_LMK_5F00_270MHz_5F00_6M75Hz.tcs

--

提前感谢、

Kiran

您好 Kiran、

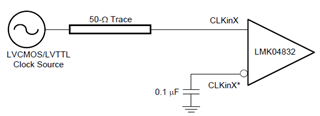

由于您具有单端同步、我建议将 CLKin0作为 MOS 输入。

我们在生产中测试 VCO 频率覆盖范围、因此即使您以最小/最大频率运行也不会出现任何问题 频率。

您有一个27MHz 域系统、我建议将 VCXO 更改为108MHz 或135MHz、以便最大限度地提高 PLL2 FPD。 借助100MHz VCXO、您可以使用的最高 FPD 仅为20MHz、PLL2的输出相位噪声将不会很出色。

LMX TCS 文件与 LMK TCS 文件相同、请向我们发送正确的 LMX TCS 文件。

图30正确。 LVDS 是电流源、因此流经电阻器的电流将在电阻器上产生电压。 如果接收器是标准 LVDS 接收器、则不需要隔直电容器。 如果接收器需要交流耦合、则图30正是您所需的。

我建议将来自 LMK PLL1的 OSCout 用作 LMX 器件的基准时钟、因为来自 PLL2的噪声将被传递到 LMX 输出。 如果 由于 CLKin2而导致 OSCout 不可用、则使用时钟缓冲器扇出 VCXO 信号。

原理图看起来不错。

Noel、您好!

抱歉、LMX TCS 文件错误、PFA 是正确的 LMX TCS 文件。

e2e.ti.com/.../7080.WBRFU_5F00_LMX_5F00_270MHz_5F00_5400MHz.tcs

[引用 userid="90437" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1049230/lmk04832-clkin0-as-sync-input/3888900 #3888900"]您有一个27MHz 域系统、我建议将 VCXO 更改为108MHz 或135MHz、以便您可以最大限度地提高 PLL2 FPD。 使用100MHz VCXO 时、您可以使用的最高 FPD 仅为20MHz、PLL2的输出相位噪声将不会非常出色。[/QUERP]关于 VCXO 频率、 根据 Mistral 的设计 、VCXO 为100MHz、 这将降低 PLL1 N / R 比率 R =1、 但 PLL2 N / R 比率不会降低、从而使 R = 1。 但是、如果 VCXO 为108MHz 或135MHz、则 PLL2 N/R 比将减小、使 R = 1、而不是 PLL1。

是否始终要求 PLL1和 PLL2的 N / R 比、以便 R 减少至1或使用 SYNC 信号足以实现时钟输出的同步?

[引用 userid="90437" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1049230/lmk04832-clkin0-as-sync-input/3888900 #3888900"]我建议使用来自 LMK PLL1的 OSCout 作为 LMX 器件的参考时钟、因为来自 PLL2的噪声将传递到 LMX 输出。 如果 由于 CLKin2而导致 OSCout 不可用、则使用时钟缓冲器扇出 VCXO 信号。[/quot]LMx 输出用于生成采样时钟、 并需要与 LMK 输出 AMS_SYSREF、PL_CLK、PL_SYSREF 和相位对齐进行同步。

我们还需要使用外部同步信号进行多时钟同步。 我们能否根据您的建议实现所需的同步?

关于 VCXO 选择、LMK04832 EVM 中使用的 VCXO 是 LVPECL 输出、但我们在设计中使用的是 LVCMOS。 输出类型变化是否会导致性能问题?

--

提前感谢、

Kiran

您好 Kiran、

PLL1的环路带宽将非常小、不需要高 FPD。 因此、如果您使用108MHz VCXO、PLL1 FPD = 1MHz、这与您使用100MHz VCXO 的情况相同。 为了降低 PLL 噪声并使环路带宽更宽、PLL2需要更高的 FPD。 如果您希望尽可能降低抖动、VCO 频率应是 VCXO 频率的整数倍。 只要相位噪声相同、LVPECL 和 CMOS VCXO 在此频率下就不会有性能差异。 SYNC 信号用于对齐所有时钟输出、它不必具有极低的噪声。

CLKout 和 OSCout 将具有一些确定性延迟(几纳秒)、在考虑到 SYSREF 频率较低的情况下、不应发布问题。 否则、您可以将 LMK 器 件置于0延迟双环路模式、以便时钟输出与 OSCout 相位对齐。

对于 LMX 配置、您可以使 FPD = 270MHz 以获得更低的带内噪声。

Noel、您好!

[引用 userid="90437" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1049230/lmk04832-clkin0-as-sync-input/3888900 #3888900"]您有一个27MHz 域系统、我建议将 VCXO 更改为108MHz 或135MHz、以便您可以最大限度地提高 PLL2 FPD。 使用100MHz VCXO 时、您可以使用的最高 FPD 仅为20MHz、PLL2的输出相位噪声将不会非常出色。[/QUERP]我不是很容易找到108MHz 或135MHz 的出色 VCXO、它具有低相位噪声和相位抖动。 您对此 VCXO 频率是否有任何推荐器件型号? 您的建议将对我们有帮助。

--

提前感谢

Kiran

你(们)好、Ajeet

我联系了几家供应商、他们还没有回复我的问题。 我介绍过的少数器件没有低相位抖动、例如 ZCU208 EVM 的 LMK04832和 CLK104板中使用的器件(LMK04832和 CLK104板中使用的器件的典型相位抖动在80毫微微秒内、而90MHz、108MHz、 135MHz 的范围为0.2ps 至1ps)。

最好使用120MHz VCXO、将 PLL VCO 的 N 预分频器作为3、R 分频器作为9、这样我的 PLL2 FPD 将为120MHz。

--

提前感谢

Kiran