大家好、

在我们的设计中、我们使用5个 LMK 的.one LMK 作为主器件、其余4个 LMK 作为从器件。

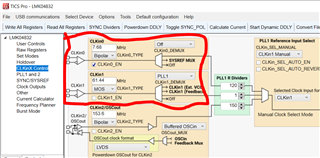

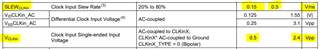

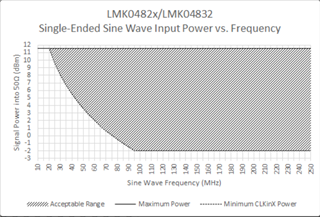

主 LMK 输入频率:49.152MHz

主 LMK 输出频率:7.68MHz

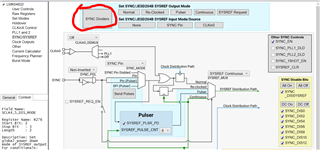

我需要选择哪种模式? 到目前为止、我正在使用双环路模式。因此、请浏览 TCS 文件和原理图、并就该模式提出建议。

在主器件中、我们得到的 CPout 为3.2V、但根据数据表(VCC/2)。

注意:环路滤波器与 EVM 相同

但我们仍然遇到 PLL1锁定问题。

e2e.ti.com/.../Master-code.tcse2e.ti.com/.../Slave-code.tcs

从机处于双循环嵌套模式 。