大家好、

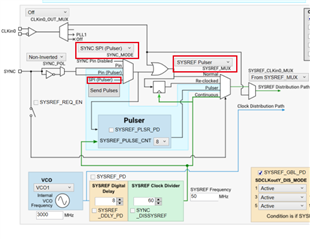

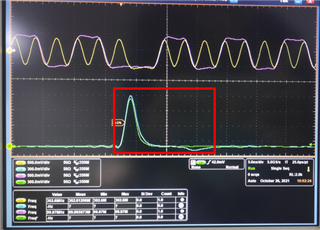

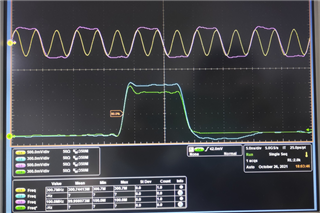

当我将 SYSREF 信号配置为"YNC SPI (脉冲发生器)"模式(图1)时、我遇到了一个新问题、但当我捕捉到该信号时、SYSREF 会像下降沿过冲一样发生变化(图2)、尽管器 件时钟是同步的。 当我禁用 SYSREF 时、siganl 为正常(图3)。 我不明白为什么?

PS:我使用10MHz 振荡器作为 PLL1输入。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Nan Li、您好!

很抱歉、上一条注释中存在错误、因为脉冲发生器模式下的 SYSREF 可以通过使用 SYNC SPI (脉冲发生器)设置的 SYNC_MODE 集生成、并向0x13E 寄存器(单击发送脉冲)写入脉冲数。

我在 SYSREF 禁用模式下不清零、并得到 SYSREF 波形。 当 SYSREF 配置为脉冲发生器模式时、它应通过发送脉冲命令生成0x13E 寄存器中提到的脉冲数。

如果您可以共享用于对器件进行编程的已用配置文件并进行检查、那将会非常好。

此致、

Ajeet Pal

您好、Ajeet、

好的、我将配置文件放在下面。

[引用 userid="256990" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1048134/lmk04828-sysref-signal-wrong-with-sync-spi-pulser-mode-lmk04828/3878598 #3878598"]我在 SYSREF 禁用模式下无法清除并获取 SYSREF 波形。SYSREF 禁用模式是、当我切换"发送脉冲发生 器"按钮时、我可以发送 SYSREF 信号、但该 SYSREF 信号不"工作"(它不会影响器件时钟、不会同步器件时钟信号、它只是一个没有任何功能的信号)。

此致、

非

Nan、您好!

很抱歉耽误你的时间、Ajeet 已经离开、所以我现在要接管。

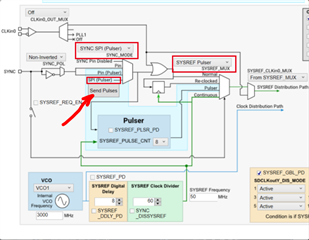

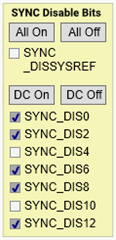

SYNC/SYSREF 路径是共享的、因此 SYSREF 信号可以复位分频器、SYNC 信号可以缓冲到 SYSREF 输出。 如果在 SYSREF 脉冲发生器上生成脉冲时清除了 SYNC_DISx 位、则会复位其他时钟。 如果在 SYSREF 脉冲发生器上生成脉冲时清除了 SYNC_DISSYSREF 位、则会复位 SYSREF 分频器、这可能导致脉冲太短。 仅当您准备中断和复位用于相位同步的通道/SYSREF 分频器时、才应清除 SYNC_DISx 和 SYNC_DISSYSREF 位。 在初始同步事件在器件时钟和 SYSREF 之间建立特定相位关系后、应设置 SYNC_DISx 位和 SYNC_DISSYSREF、以防止分频器在 SYSREF 脉冲发生时复位。

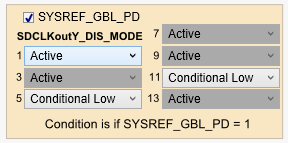

这可能不是问题、但出于完整性考虑:您还可以使用 SYSREF_GBL_PD 位将 SYSREF 输出保持在低电平或在发生同步事件时保持在共模电压、以防止同步脉冲通过 SYSREF 输出进行缓冲。 这实际上是一个"静音"控制、因此 LMK04828上的同步事件不会意外地被解释为要计时的器件上的 SYSREF 事件。

分频器复位过程在使用 SYSREF 之前进行、并在器件时钟和 SYSREF 之间建立相位关系、可简化为:

一旦分频器被复位、SYSREF 触发应该是简单的:

此致、

Derek Payne